### Overclocking...

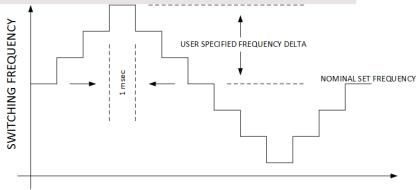

### **Fsw Spread Spectrum**

Frequency will step up and down between a Maximum **Max Fsw** and a Minimum frequency **Min Fsw.** Step size will depend on number of phases and the set duration

# **Enable Fsw Spread Spectrum**

If marked the frequency will shift between a max and a min value with a selectable repetition frequency

## Fsw Spectrum Sweep Duration

How long time for a full cycle of frequency change

TIME

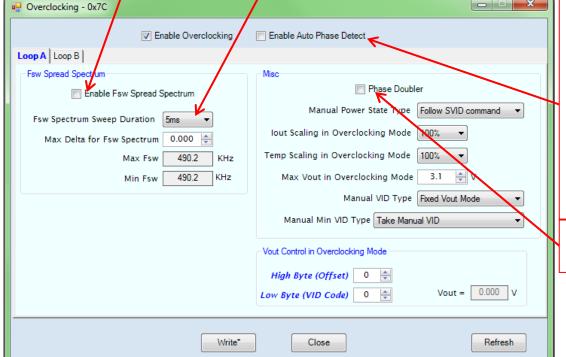

#### **Enable Auto Phase Detect**

XDPE10281 is capable of supporting automatic detection of populated phases by measuring the PWM pin voltage after VR\_EN assertion, driver VCC POR and VIN greater than the VIN 'ON' Threshold

Phases must be populated from lowest to highest

Unpopulated PWM pins must be open (floating)

A momentary weak pull down will be applied when the PWM pin voltage is sensed

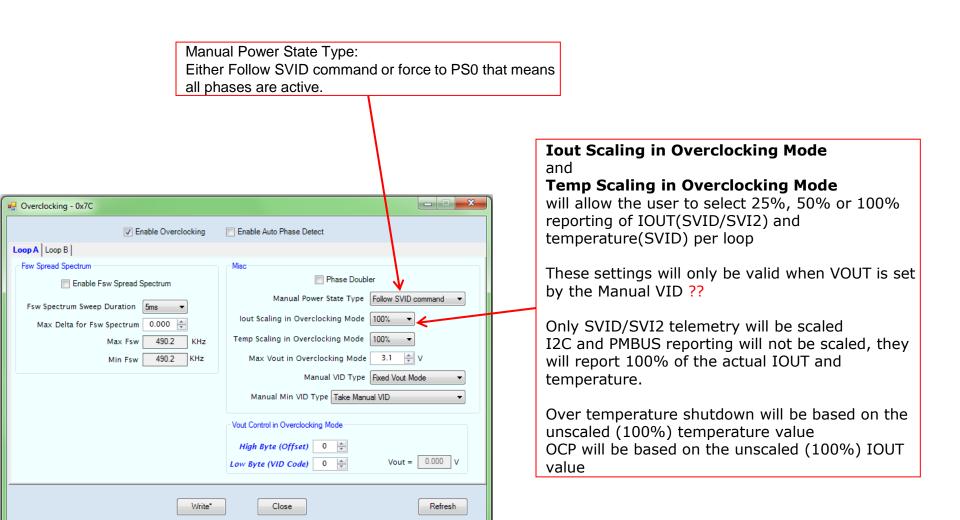

#### **Phase Doubler**

Tick if using dual powerstages per phase with a splitter for the PWM signal

### Overclocking...

## Overclocking...

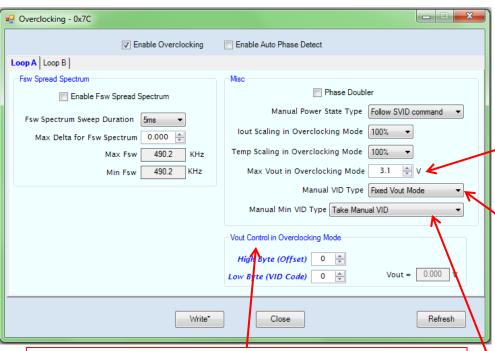

### Vout control in overclocking mode

Allow MANUAL VID settings

Offset: can be + or - offset

**VID code:** Vout follows the AMD VID table except for 0 that will cause VOUT to return to the SVID/SVI2 commanded voltage

This functio also work in non overclocking mode to manually enter VID code to set Vout.

NOTICE if Vout been set by a SVI2 command then it is not possible to set a lower output voltage than that command set.

### Max Vout in Overclocking Mode:

Allow a maximum Vout to be set. Any command to set a higher Vout will be ignored and actual Vout will stop at the selected voltage even if commanded to go higher

### Manual Min VID type

Select between Take Manual VID orTake MAX of SVID or MAN VID

#### Manual VID type:

**Fixed Vout Mode**

Fixed offset mode

In 'Fixed VOUT' Mode, VOUT is set by the VID code specified by the operating mode.

In 'Fixed VOUT' Mode, the SVID ALERT# will assert immediately upon receipt of an SVID command to change VOUT.

Because VOUT will not change, T\_alert assertion will <u>not</u> be delayed by VID\_DELTA/SLEW\_RATE

In AMD SVI2, VOTF Complete will not assert in Fixed VOUT mode

In 'Fixed VOUT' Mode, changes to the Manual VID register will cause VOUT to change but will not cause SVID ALERT# to assert.

Writing the Manual VID register to 0 will cause VOUT to return to the SVID/SVI2 commanded voltage