# nVidia

## Purpose

Describe the settings needed to run in nVidia mode

Target audience:

Design engineers that have some experience with digital power and nVidia needs as the explanations focus on settings in XDPE12xxx and XDPE 14xxx family of controllers.

**Infineon Proprietary**

#### nVIDIA PWM VID Overview

A pulse width modulated I/O that controls the Voltage Regulator VID set point (output voltage) by modulating the duty cycle of the signal sent

- PWM VID functionality applies to Loop 0 only

- An optional method of control is to digitize an analog voltage (VAUX) and generate an output voltage proportional to this input.

## PWM VID implementation allows for

- Wider range of VID set points using a single I/O pin

- VID target change can be communicated in a single cycle

- PSI entry/exit is instantly communicated

**Infineon Proprietary**

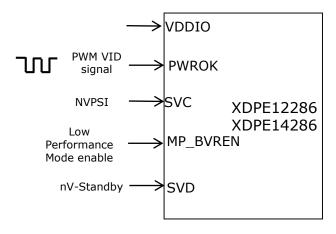

## nVidia PWM VID connections

In nVidia PWM mode some pins get a new function in parts that do support the PWM-VID function

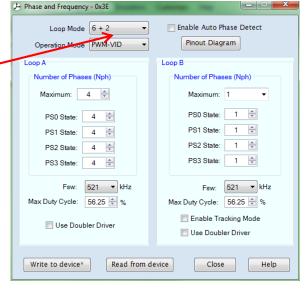

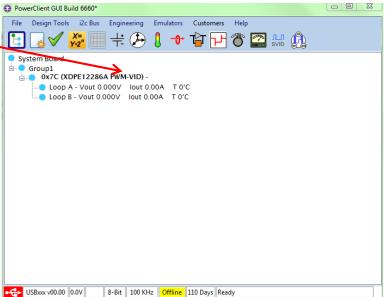

## Select nVidia mode

Select the PWM-VID to enter nVidia mode

The selected mode is visible after the component name

**Infineon Proprietary**

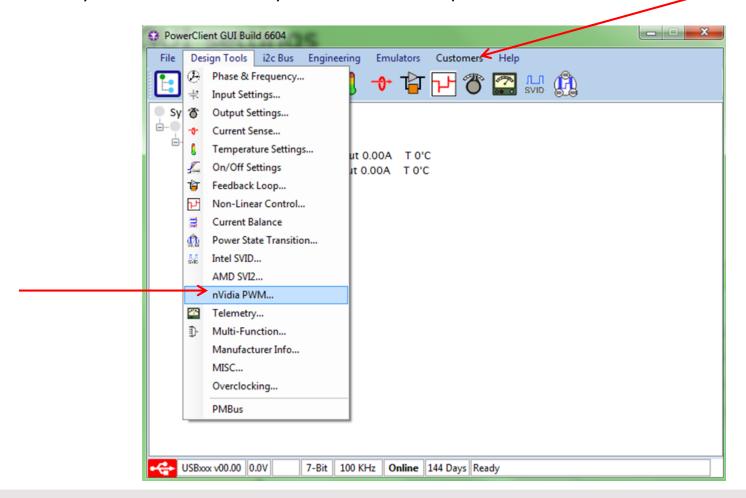

# Find nVidia settings in GUI

You may need a password to activate the nVidia settings. Enter it in the Customers tab Ask your Infineon FAE if you do not have a password.

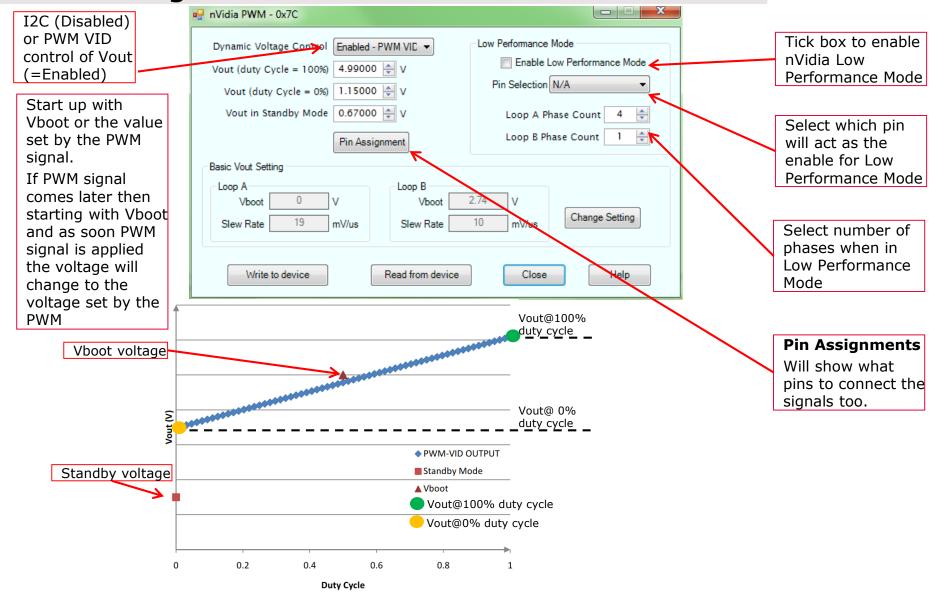

## GUI settings

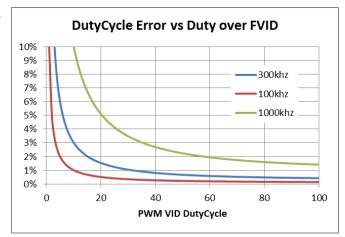

# Sierra Digital Solution

- Digital NVPWM connect directly to the SVD pin

- Signal digitized by 100MHz clock (10ns resolution)

- Typical FVID 300kHz

- Usable FVID range 100kHz ←→3MHz

Digital offset can be added via I2C

# Digital PWMVID Measurement

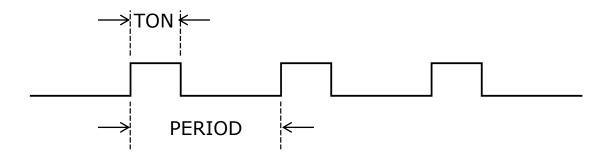

- The dutycycle is calculated as the quotient of the ON time of the NVPWM over the PERIOD of the signal.

- ON time is measured from the rising edge to the falling edge of the NVPWM

- PERIOD is measured from a rising edge to the next rising edge

- The calculation is updated on every rising edge of NVPWM

- A continuous moving average of 4 dutycycles calculations is used to set the target voltage

# **Digital Solution Equations**

- Duty = Ton/Period

- Vout = vout\_vid\_vmin + duty · pwm\_vid\_slope

- pwm\_vid\_slope = (Vmax-Vmin)/(5mV(VIDtable)) per 100% duty cycle change

## Other notes

The SVC pin is used for the NVPSI function. Pulling the pin low would set the VR to a low power state

## nVidia PWM... Slewrates

- Digital solution

- the slewrate can be set in the Output Settings window. The fast slew rate setting is used.

# **Revision History**

2.0: Added XDPE142xx information