# PowerClient GUI User Guide

AN003-V2.0

Applications Team April-20

IN PROGRESS BEEING UPDATED

- 1 Purpose

- 2 Supported devices

- Install GUI software

- 4 Main GUI window

- General error messages and warnings

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- 14 Nonlinear control

- 15 Current balance

- Power state transitions

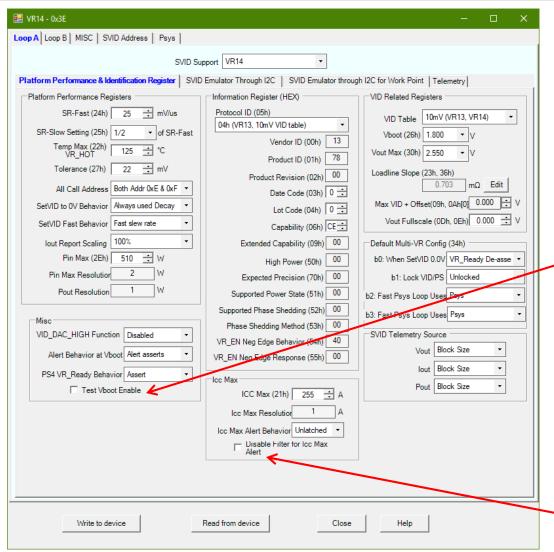

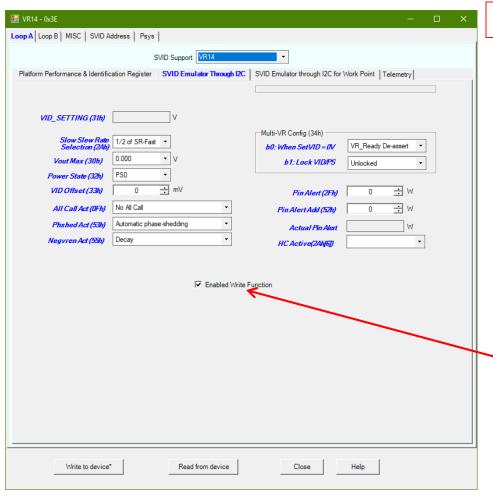

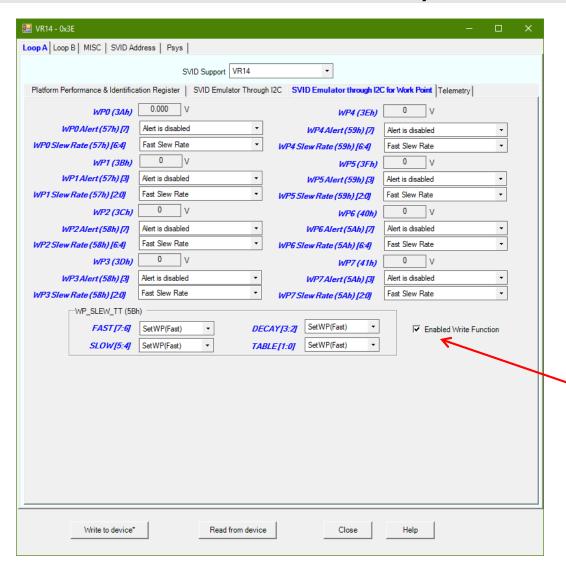

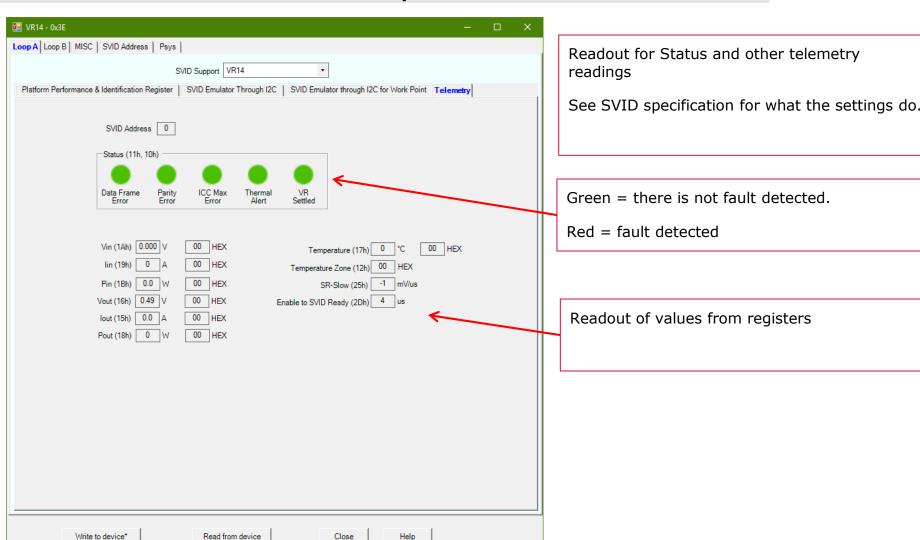

- 17 Intel SVID XDPE122xx

- 18 Intel SVID XDPE142xx

- 19 AMD SVI

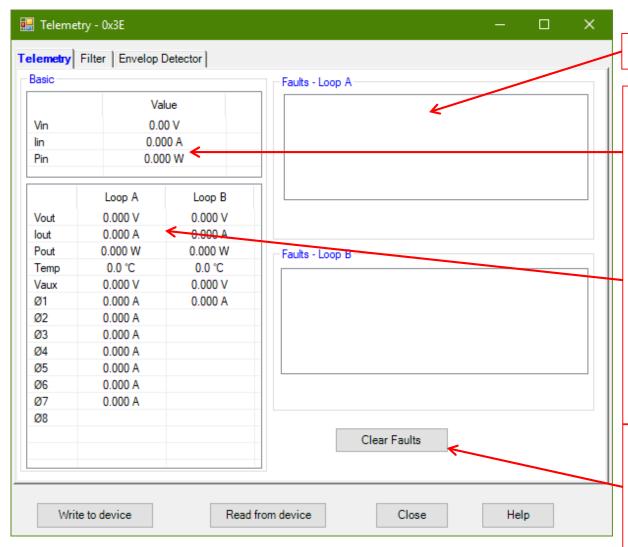

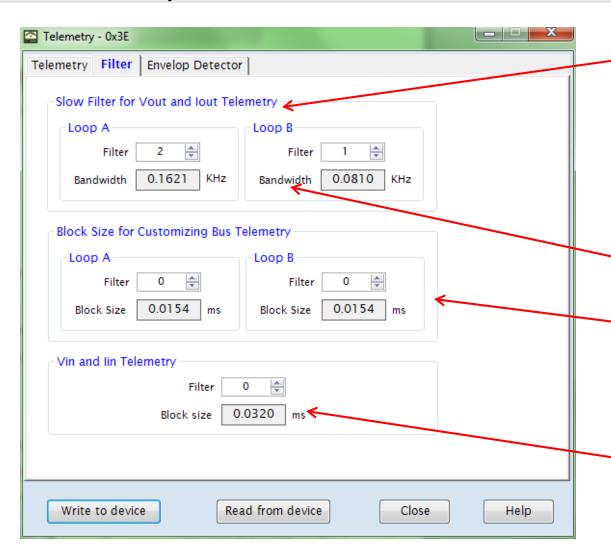

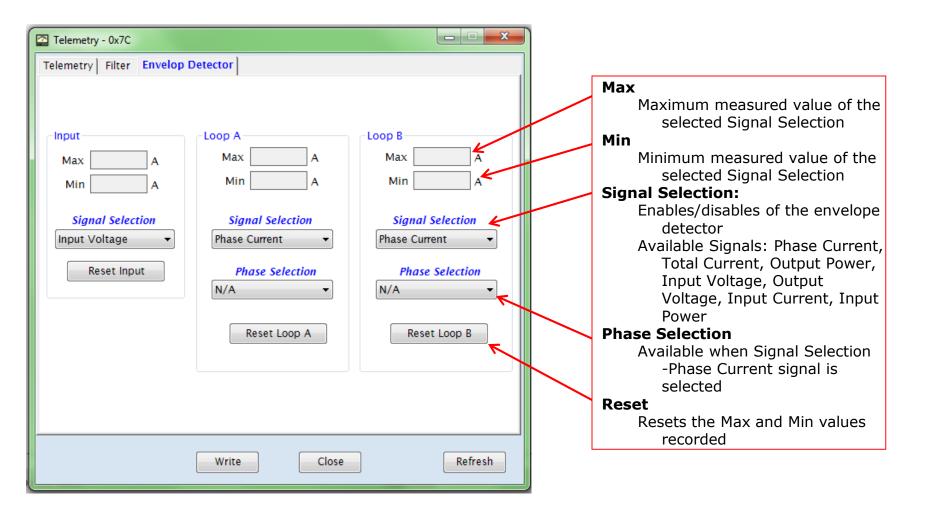

- 20 Telemetry

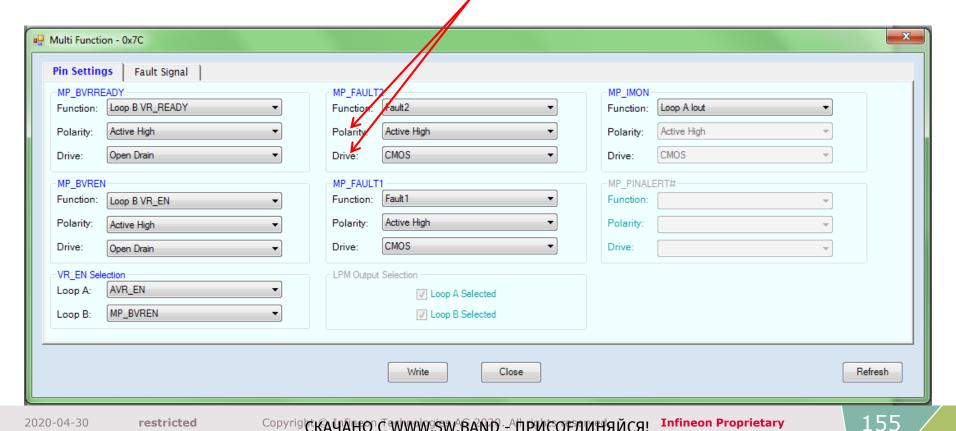

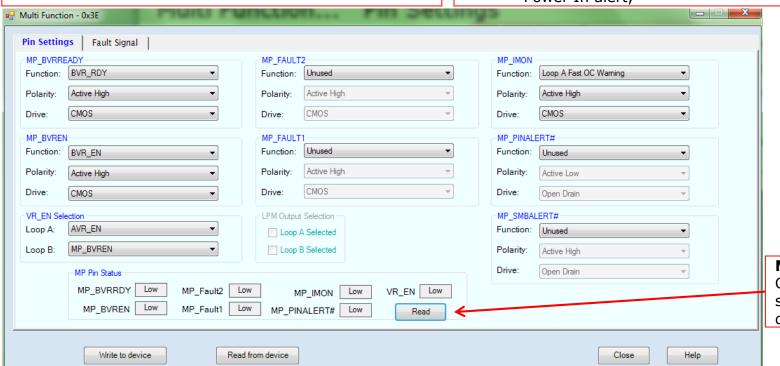

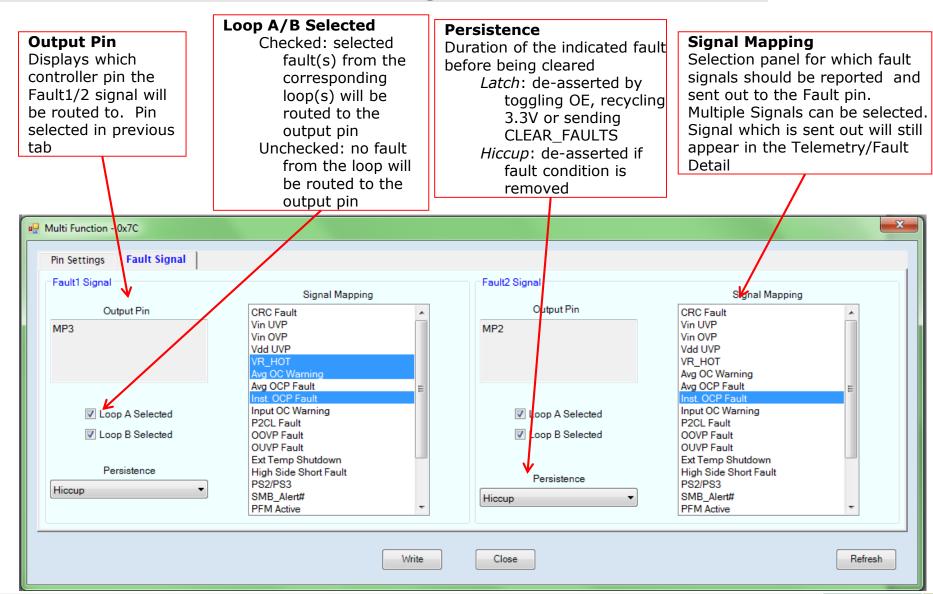

- 21 Multi Function

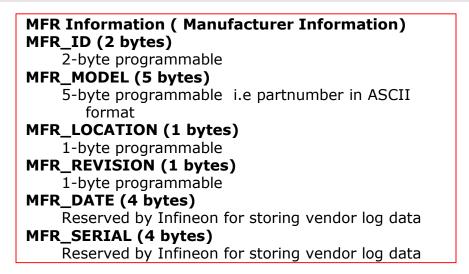

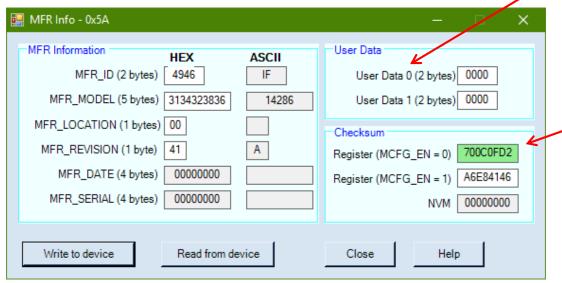

- 22 Manufacturer info

- 23 MISC

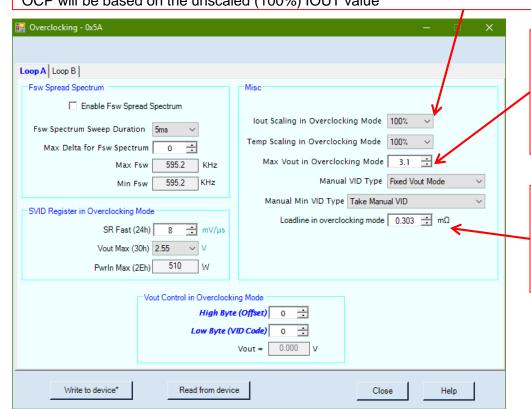

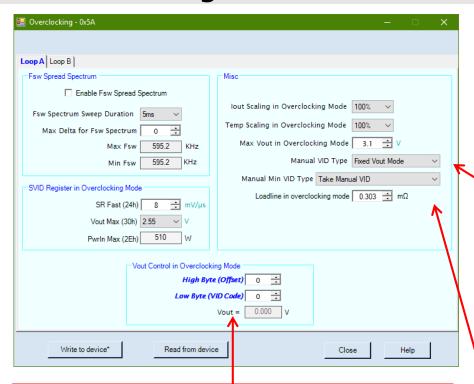

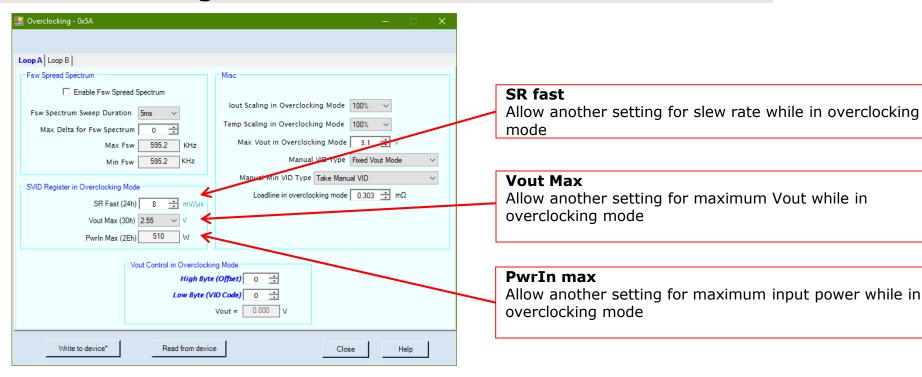

- 24 Overclocking

25

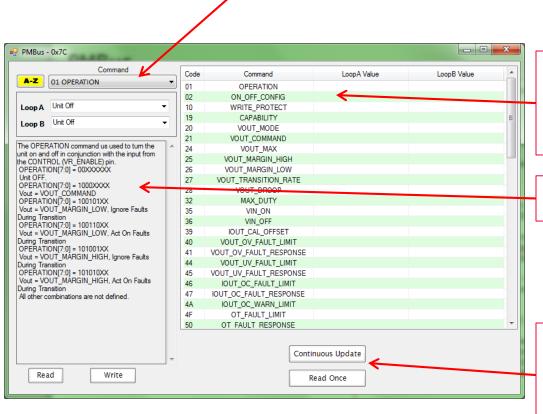

**PMBus**

26

Customer specific

- 1 Purpose

- 2 Supported devices

- 3 Install GUI software

- 4 Main GUI window

- 5 General error messages and warnings

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

### **Purpose**

- This document describes the steps and settings to create a configuration file for the XDPE122xx and XPDE142xx family of multiphase controllers.

- Both AMD, Intel, PWM-VID settings are shown. Different parts of the family support all or only a few of the settings.

- Each window in the GUI tool will be explained.

- Target audience: Design engineers with knowledge of tuning feedback loops for Intel and AMD settings.

- 1 Purpose

- 2 Supported devices

- 3 Install GUI software

- 4 Main GUI window

- 5 General error messages and warnings

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

## Supported Devices

| Sierra B/C |           | Sequoia   |

|------------|-----------|-----------|

| XDPE12250  | XDPE12283 | XDPE14283 |

| XDPE12254  | XDPE12284 | XDPE14284 |

|            | XDPE12286 | XDPE14286 |

- 1 Purpose

- 2 Supported devices

- 3 Installation procedure

- 4 Main GUI window

- General error messages and warnings

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

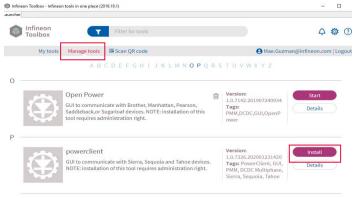

### Installation procedure

- Two ways to download/update the GUI

- Infineon Toolbox available at <a href="http://www.infineon.com/toolbox">http://www.infineon.com/toolbox</a>

- Follow the instructions listed to download and install the Infineon Toolbox

In the Infineon Toolbox, go to Manage tools and select PowerClient's Install or Update button.

- MyICP (My Infineon Collaboration Platform)

- Register and login to your MyICP account

- Once logged in, go to <a href="https://myicp.infineon.com/sites/enterprise power/">https://myicp.infineon.com/sites/enterprise power/</a>

- > There may be a need to install latest license file. Ask your Infineon FAE for the latest one

- copy the license file IR DPDC License.txt into the installation directory

NOTE: Infineon toolbox is the fastest way to have access to the GUI as it doesn't need internal clearing of the user.

- 1 Purpose

- 2 Install GUI software

- Main GUI window

- 4 General error messages and warnings

- Start to create a configuration file

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

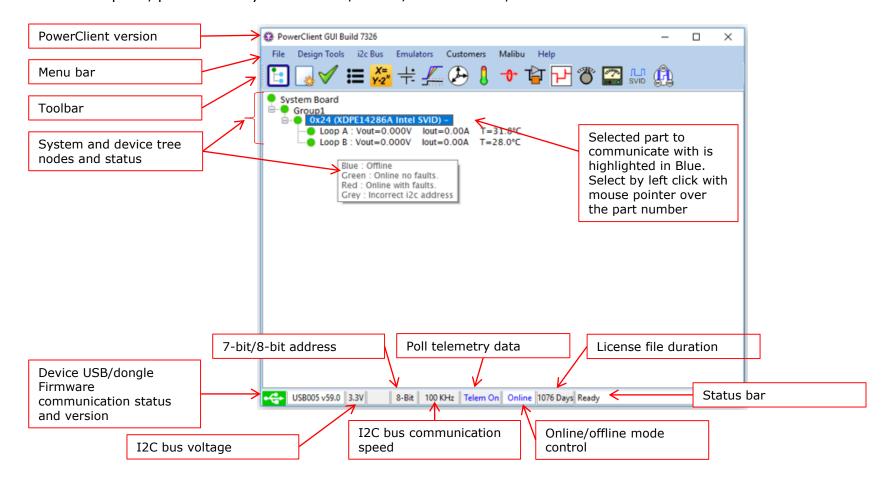

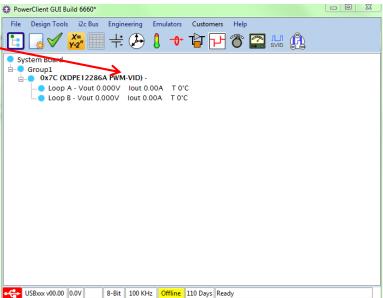

### Main GUI window

PowerClient main dialog displays and consists of GUI version, menu bar, toolbar, system and device tree nodes and status, USB/dongle Firmware communication status and version, I2C bus voltage, 7-bit8-bit address display, I2C bus communication speed, poll telemetry data status, online/offline status, GUI license file duration and status bar.

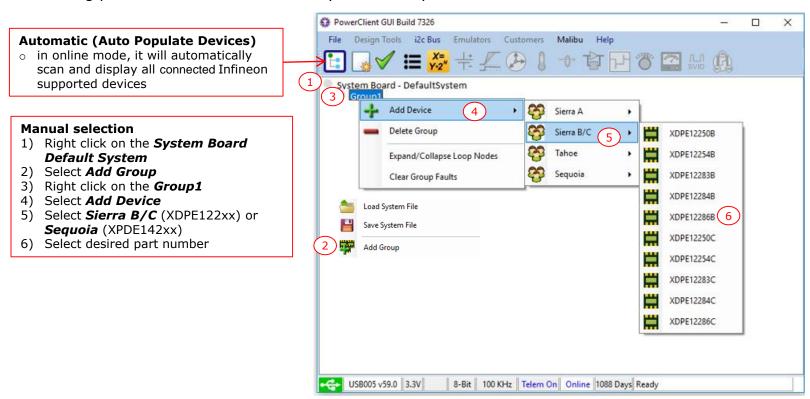

### Main GUI window: Starting the GUI

- When you first launch the GUI after installation, it will have an empty System Board window.

- Adding parts can be done automatically or manually.

- The GUI will use the last system tree node setup as a default in the next GUI launched.

- > If the USB dongle is connected, it will try to sync available devices listed in the main GUI window.

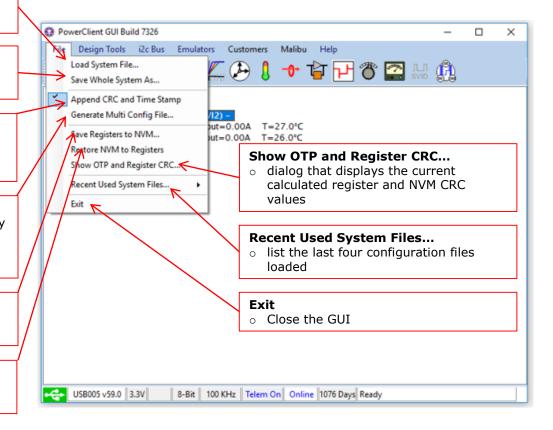

## Main GUI window: Menu bar (File)

### Load System File...

loads the whole system and device register configuration data

### **Save Whole System As...**

saves the whole system and device configuration data

### **Append CRC and Time Stamp**

if checked, it appends the CRC and time stamp to the file name when a configuration file is saved

### Generate Multi-Config File...

generates a multi-config file to simplify the need or ordering/keeping track of devices with different configuration files

### **Save Registers to NVM...**

dialog that will allow the user to perform a NVM upload

### **Restore NVM to Registers**

Dialog that will allow the user to perform a NVM upload

16

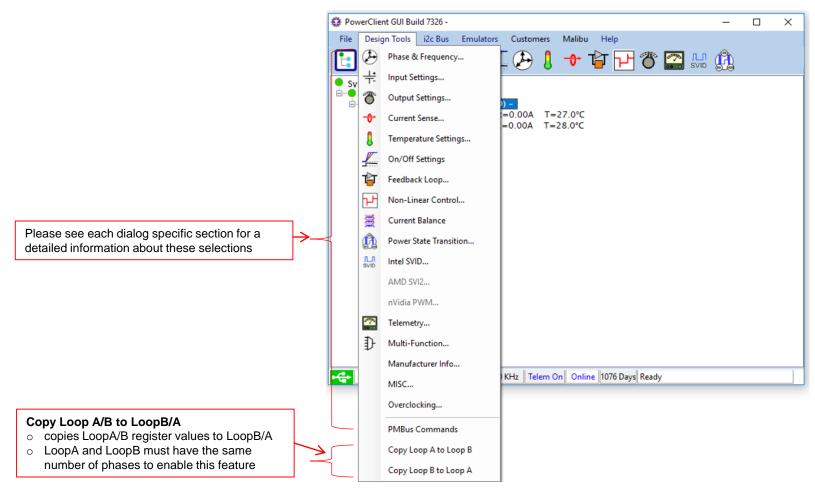

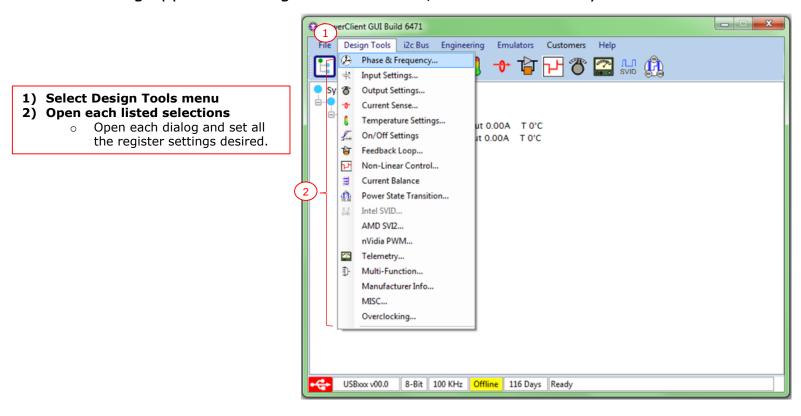

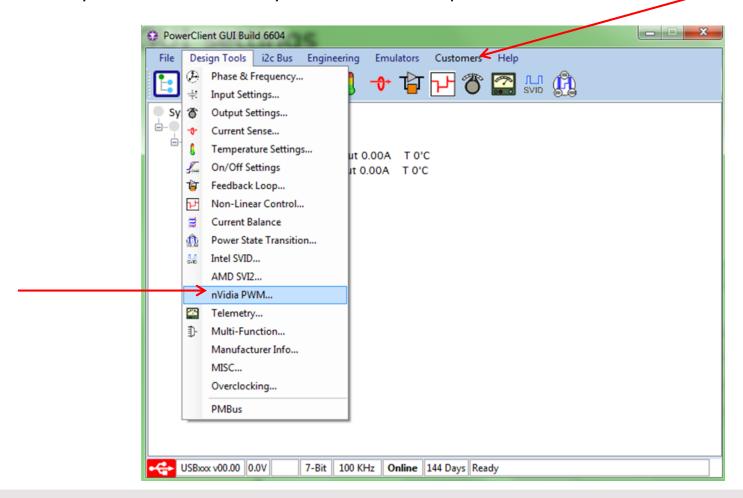

## Main GUI window: Menu bar (Design Tools)

Design tools contain all the tools and utilities needed to configure the device.

NOTE: User must have selected a part in Device Node (blue highlighted background) to be able to select any design tool.

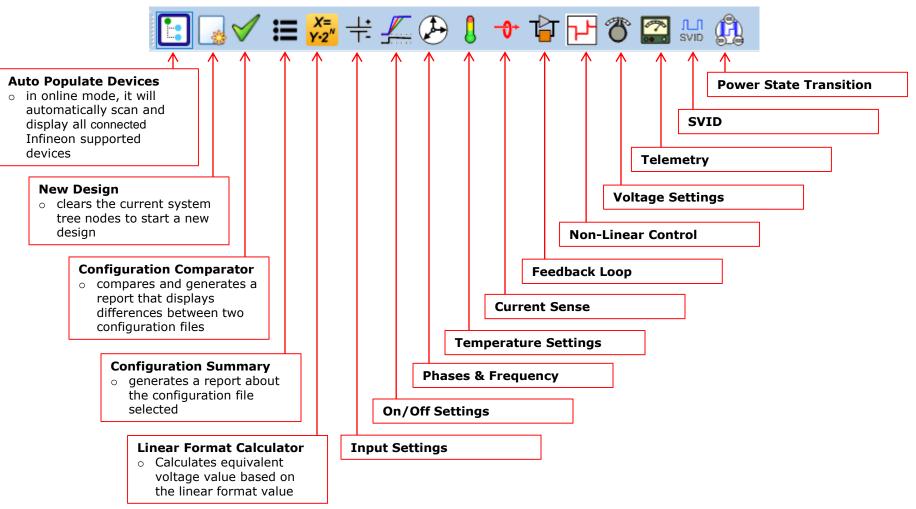

### Main GUI window: Toolbar

> Toolbar provides shortcuts of the most frequently use basic operations and control dialogs.

NOTE: Some controls are disabled unless the device node (part at specific address)is selected.

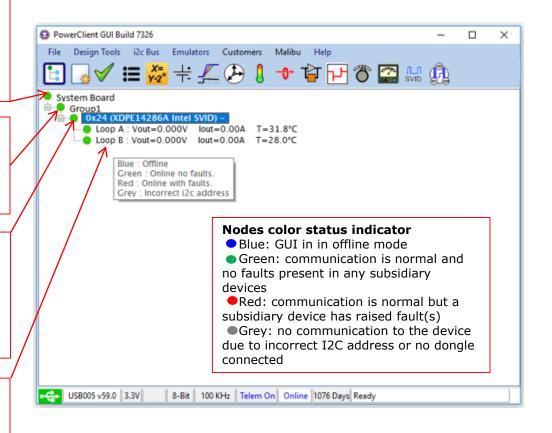

## Main GUI window: System tree nodes

> System tree nodes list all the devices in the system and how they are arranged into groups.

#### System node

- root node that represents the entire system board

- user can add group(s), save and load board design, or do other board-level functions by right clicking on the node

#### **Group node**

- group of devices that may contain single or multiple devices

- user can add device(s), delete group, or do other group-level functions by right clicking on the node

#### **Device node**

- individual device that specifies device slave address, part number and operational mode

- user can load and save specific device configuration file, delete device, or do other device-level functions by right clicking on the node

### Loop node

displays device's output voltage, output current and temperature per loop

### Main GUI window: Communication and license

#### I2C bus communication speed A PowerClient GUI Build 7326 X base speed is 100KHz File Design Tools i2c Bus Emulators Customers Malibu Help $\circ$ can be change in the *i2c Bus* → *i2c* ■ 🛵 岩 🚣 🕭 🚶 💠 🖆 🔁 🎖 🎑 👑 🐧 Address Scanner ensure that the target device(s) show System Board up in the list to verify that the Group1 0xB4 (XDPE14286A AMD SVI2) communication is stable at the selected Loop A: Vout=0.000V | lout=0.00A T=28.0°C speed after the Scan i2c/PMBus Loop B: Vout=0.000V lout=0.00A T=29.0°C Address button is selected 7-bit/8-bit I2C address 8-bit is the base i2c address display o can be change in the *i2c Bus* → *Use* 8-bit i2c Address **USB/Dongle FW status** Poll telemetry data o Green: dongle is detected Telem On: continuously poll telemetry data o Red: either the dongle is not connected or Telem Off: telemetry data will only update the driver is not correctly installed when Read from device is selected **USB/Dongle FW version** o if the dongle is detected and communicating correctly, it will display the hardware and USB005 v59.0 3.3V 8-Bit 100 KHz Telem On Online 1076 Days Ready Firmware version. o if the version is **v0**, there may be an issue Status bar License file duration with the driver Displays if the current communication status list remaining days before the GUI license o user needs to update its Firmware version if between the GUI and the device will expire a newer USB dongle firmware is available Contact your Infineon FAE

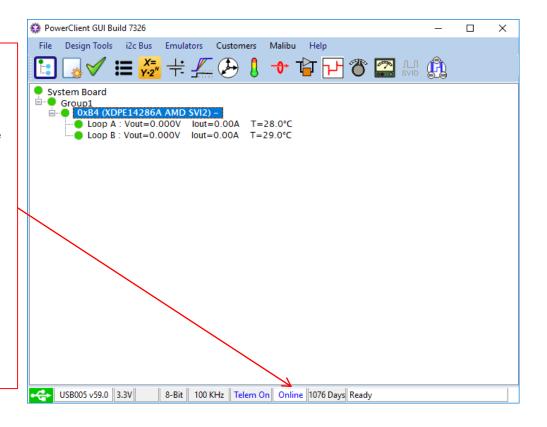

### Main GUI window: Online/offline mode control

#### Online mode

- GUI will attempt to communicate to the device

- o If device is detected, user can

- o modify contents of the device

- load contents of a configuration file into the device

- Save contents of the devices' registers into NVM

- Restore NVM contents into the registers

- o Poll telemetry data

- o If device cannot be detected

- Write and read from the device will be disabled

#### Offline mode

- Write to internal cache register only and not to the device, regardless of the connection status

- Can be use as a system file editor or a system file viewer

- 1 Purpose

- 2 Install GUI software

- 3 Main GUI window

- 4 General error messages and warnings

- Start to create a configuration file

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

### General errors, warnings and reminders

- When a change is made in a dialog

- Write to device button will change to Write to device\* to indicate that changes have been made to the dialog.

- Write to device\* needs to be selected to commit the changes.

- o In online mode, all changes made will be written into the device.

- o In offline mode, all changes made will be written to the internal cache register only and not to the device.

- Error checking to make sure no design rule is violated

- - An example is a value entered it out of range.

- Write button is disabled when error(s) is present.

- Tabbed dialog name will also turn red when error is active to show which tabbed dialog has the error.

- Marning: yellow indicator flags a warning

- A warning means the input value may cause non-optimal performance.

- Warnings do not prevent the GUI from committing changes to the device.

- Hovering the cursor over the error sign will display explanation of the warning.

- Blue dialog fieldnames

- It indicates that there is no register associated with it.

- Values are only save as a system configuration data.

- It is only use for simulation and/or calculation.

- Disabled or greyed out dialog fields

- o It is for information only and maybe a calculated data from another window.

- It can also be enabled/disabled depending on the part number.

**NOTE**: Data must be entered and written one dialog at a time. If data is being modified on two or more dialogs, pressing the **Write to device** button will only write data on the current dialog. Other change(s) data made on the other dialog(s) will be gone.

### Often used selection

### Write to device

- In online mode, all changes made will be written into the device.

- In offline mode, all changes made will be written to the internal cache register only and not to the device.

### Read from device

- In online mode, it will restore and refresh dialog field values based on its current associated register value.

- In offline mode, it will restore and refresh dialog field values based on its associated internal cache register value.

### Close

Close the window

### Help

Open up the GUI user guide

### > Shutdown Response / Response

- o **Ignore**: fault is ignored

- Latch: Shuts down the HS and LS FETs

- Hiccup: Shuts down HS and LS FETs and controller will attempt to restart the system in hiccup manner

- 1 Purpose

- 2 Install GUI software

- 3 Main GUI window

- 4 General error messages and warnings

- Start to create a configuration file

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

## Steps to create a start-up configuration file

- > Easiest is to start by using an existing approved config file and modify the parameters that differ.

- Ask your Infineon FAE for a reference config file.

- If no existing approved config file is available, user can manually create one.

- 1 Purpose

- 2 Install GUI software

- 3 Main GUI window

- 4 General error messages and warnings

- 5 Start to create a configuration file

- 6 Phase & Frequency

- 7 Input settings

- 8 Output settings

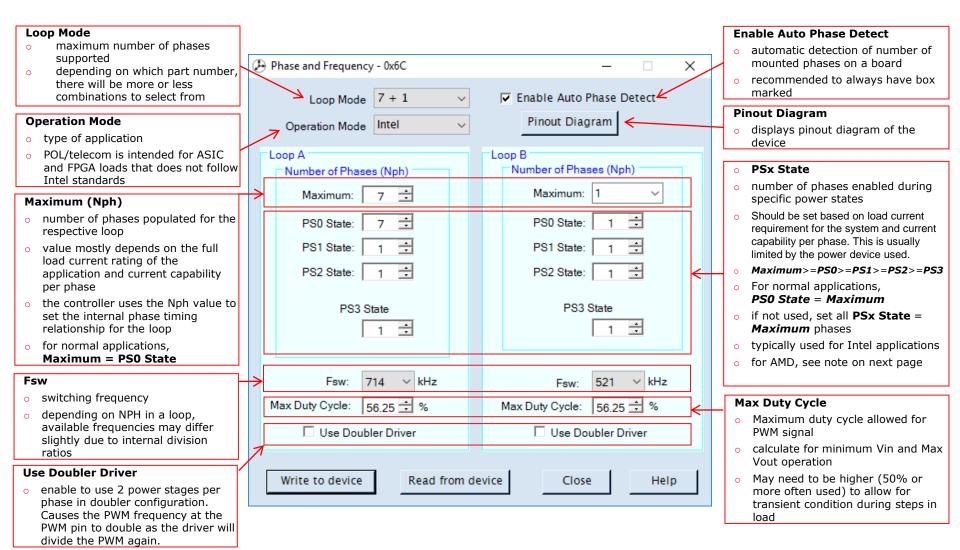

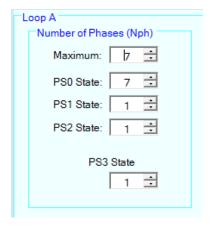

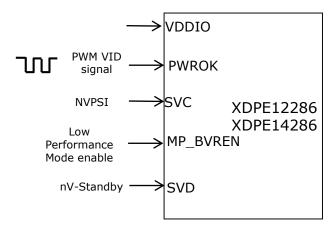

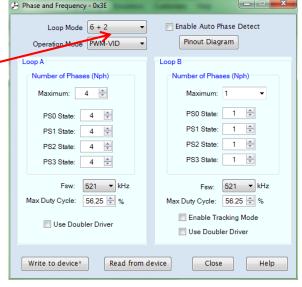

## Phase & Frequency

## Phase & Frequency

- For AMD, the power states translate to

- PS0 State=normal operation

- PS1 State=PSI0\_L

- PS2 State=PSI1\_L

- PS3 State= Not Used (set to same as PS2)

Note: GUI does not change the text for different modes like AMD. It always uses the Intel names.

- 1 Purpose

- 2 Install GUI software

- 3 Main GUI window

- 4 General error messages and warnings

- 5 Start to create a configuration file

- 6 Phase & frequency

- 7 Input Settings

- 8 Output settings

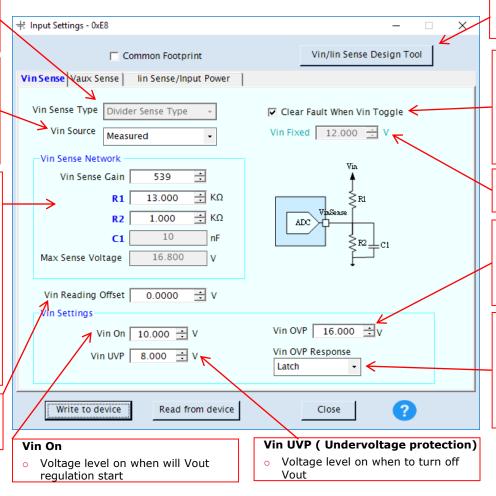

### Input Settings... Vin Sense

#### **Vin Sense Type**

Vin Sense method that can be modified in the **Iin Sense/Input** # Input Settings - 0xE8 **Power** tab

#### Vin Source

- Measured: Vin telemetry will be based on the sense result on the Vin sense pin

- Vin Fixed: Vin telemetry will be a fixed value entered in the Vin Fixed dialog field

#### Vin Sense Network:

When Vin is set to *measured*, an external resistor divider is needed.

#### Vin Sense Gain

gain factor and will depend on the resistor divider resistance

#### R1, R2

• Typical values are 19.1kΩ/1.54kΩ or  $13k\Omega/1k\Omega$

#### **Max Sense Voltage**

- Default should be ~16V for a 12V nominal VIN application

- Value depends on the resistor divider resistance

#### Vin Reading Offset

Used to compensate for offset error in the VIN sense for a more accurate VIN telemetry

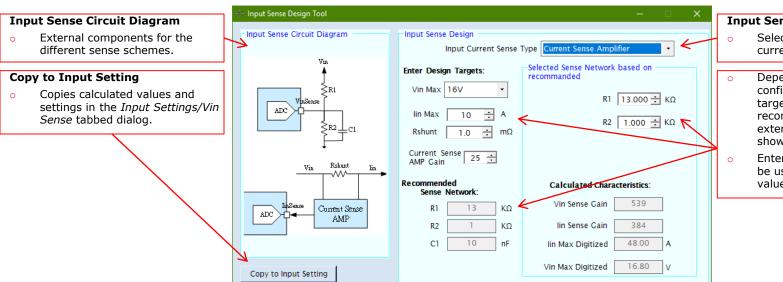

### Vi/Iin Sense Design Tool

Opens the <u>Input Sense Design</u> <u>Tool</u> that helps calculate settings

#### **Clear Fault When Vin Toggle**

- Checked: Vin toggle ( Vin go away and comes back) can reset fault conditions just like the action of toggling VR\_EN can reset fault conditions

- Unchecked: only toggling VR\_EN can reset fault conditions

#### Vin Fixed

Vin telemetry value when **Vin Source** is set to *Vin Fixed*

### Vin OVP (overvoltage protection)

- Voltage level on when the regulator stop switching to protect power stages and load

- Maximum value is based on the "Max Sense Voltage" value

### Vin OVP Response

- Ignore: Vin OVP fault is ignored

- Latch: Shuts down HS and LS FETs

\* enable pin or Vin need to be

toggled to restart

- Hiccup: Shuts down HS and LS FETs and will automatic retry once fault is gone

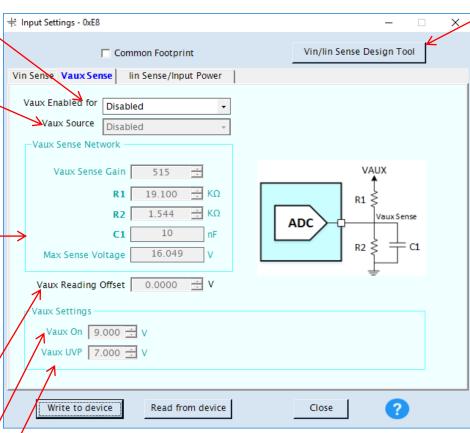

### Input Settings... Vaux Sense

### Vaux Enabled for Options to enable it in LoopA, LoopB and both LoopA/B If this function is not used, set it to disabled **Vaux Source** pin to be used to sense the Vaux voltage **Vaux Sense Network Vaux Sense Gain** Gain factor to get correct voltage reading Typical value is 515 but depends on the resistors and board layout R1, R2 • Typical values are 19.1kΩ/1.54kΩ Max Sense Voltage Default should be ~16V for a 12V nominal VIN application Value depends on the resistor divider resistance Vaux Reading Offset Used to compensate for offset error in the Vaux sense for a more accurate Vaux telemetry Vaux On Voltage level on when will Vout regulation start assuming Vin also is above its threshold

#### Vi/Iin Sense Design Tool

Opens the <u>Input Sense Design</u> <u>Tool</u> that helps calculate settings

Voltage level on when to turn off

**Vaux UVP**

Vout

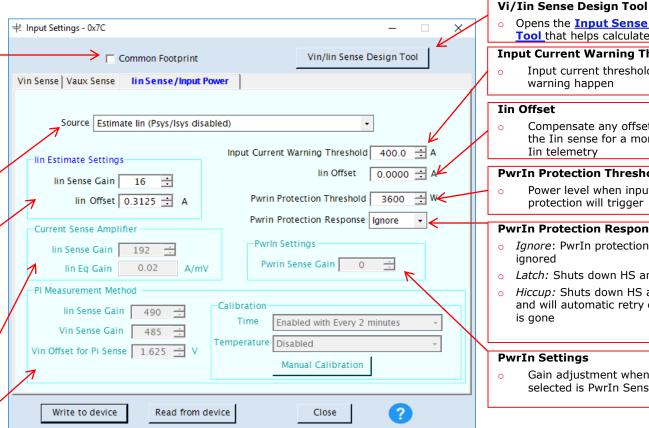

### Input settings... Iin Sense/Input Power

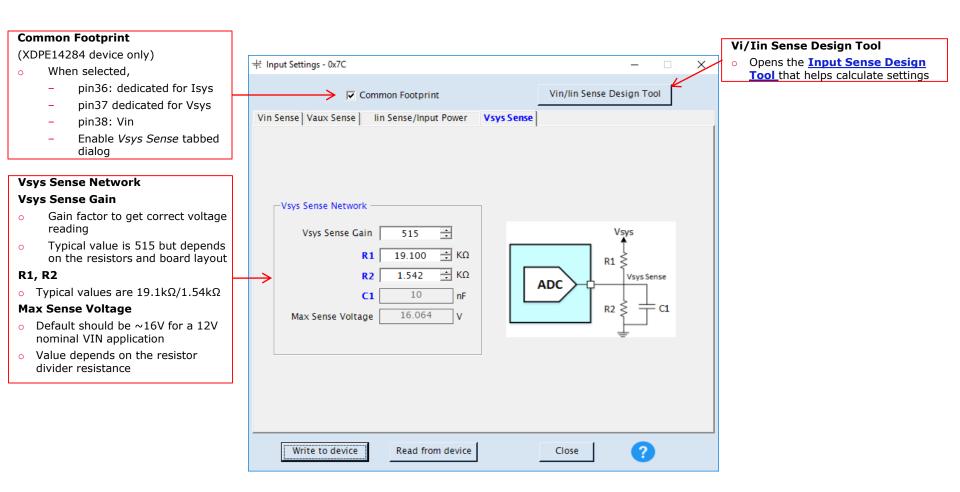

### **Common Footprint** (XDPE14284 device only)

- When selected,

- pin36: dedicated for Isys

- pin37 dedicated for Vsys

- pin38: Vin

- Enables Vsys Sense tabbed dialog

#### Source

- Selection of how input current is measured

- Disabled, Calculated, PI Sense,...

- Selection list is based on the selected part numbers.

#### **Iin Estimate Settings**

- Calculates the input power that depends on real efficiency, Iout, Vin, duty cycle and losses.

- Values should be changed to make reported Iin match the external measured Iin.

### **Current Sense Amplifier**

Gain adjustments for the sensed signal when **Source** selected is set to be Iin Sense Amplifier.

#### **PI Measurement Method**

- Gain adjustments for the sensed signal when **Source** selected is set to be PI Sense.

- **Calibration**: sets the calibration cycle and can compensate temperature drift and more.

Copyrig CKAYAHO C WWW.SW.BAND - ATTPHEOEDINHANCA!

Opens the **Input Sense Design Tool** that helps calculate settings

#### **Input Current Warning Threshold**

Input current threshold when

Compensate any offset error in the Iin sense for a more accurate

#### PwrIn Protection Threshold

Power level when input power protection will trigger

#### **PwrIn Protection Response**

- *Ignore*: PwrIn protection fault is

- Latch: Shuts down HS and LS FETs

- Hiccup: Shuts down HS and LS FETs and will automatic retry once fault

Gain adjustment when **Source** selected is PwrIn Sense.

## Input settings... Vsys Sense (XDPE14284 only)

Note: This tabbed dialogue is only visible on a XDPE14284 device and when **Common Footprint** is selected.

## Input settings... Input Sense Design Tool

#### Input Sense Type

- Selects which type of input current sensing will be use.

- Depending on selected configuration entered design target numbers and calculation of recommended values for the external components will be shown.

- Enter the resistor values that will be used. Typical the recomended values.

- 1 Purpose

- 2 Install GUI software

- 3 Main GUI window

- 4 General error messages and warnings

- 5 Start to create a configuration file

- 6 Phase & frequency

- 7 Input settings

- 8 Output settings

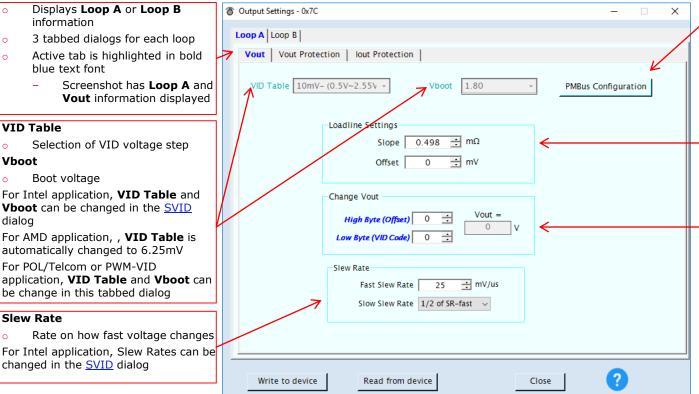

### Output Settings... Vout

Displays Loop A or Loop B information 3 tabbed dialogs for each loop Active tab is highlighted in bold blue text font Screenshot has Loop A and **Vout** information displayed **VID Table** Selection of VID voltage step Vboot Boot voltage For Intel application, VID Table and **Vboot** can be changed in the SVID dialog For AMD application, , VID Table is automatically changed to 6.25mV For POL/Telcom or PWM-VID application, VID Table and Vboot can be change in this tabbed dialog Slew Rate Rate on how fast voltage changes

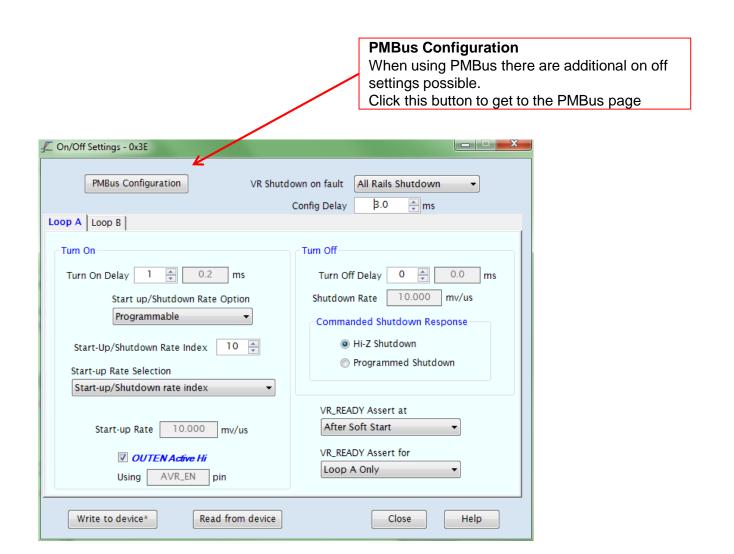

#### **PMBus Configuration**

Opens the PMBus Configuration dialogue that is use to send PMBus commands to set Vout.

### **Loadline Settings**

#### Slope

Use to define how much Vout is adjusted by load current

#### Offset

- Use to position the Vout with a fixed offset over the all load currents

- Typical value is 0mV

#### Change Vout

Manual control of Vout

### High Byte (Offset)

- Adds an offset to existing Vout

- Values >80 count converts to a negative number

### Low Byte (VID Code)

- Sets a VID code for a specific Vout

- Any settings that is not 0 will override other voltage commands

changed in the SVID dialog

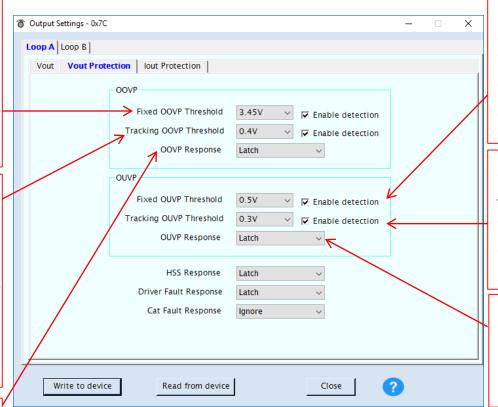

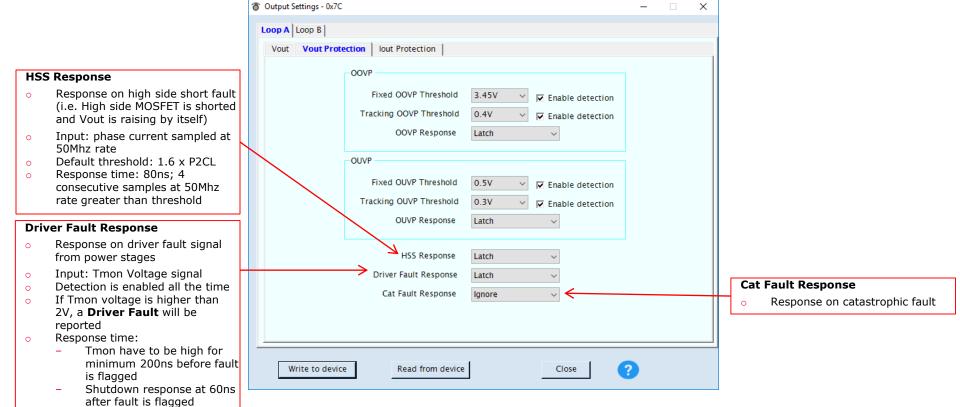

# Output Settings... Vout Protection

### Enable detection (Fixed OOVP)

Enable/disable Fixed OOVP

Threshold detection

#### Fixed OOVP Threshold

- Threshold that determines if Vout is over voltage

- Triggered when Vout > Fixed OOVP Threshold

- Always active after the initialization state except during open sense line fault detection

- Recommended setting is <output cap rating and >Vout Max

#### **Enable detection** (Tracking OOVP)

Enable/disable tracking OOVP

Threshold detection

#### **Tracking OOVP Threshold**

- Threshold is based on the difference between Vout and Vtarget.

- Triggered when (Vout Vtarget) > Tracking OOVP threshold

- Enabled during soft start, calibration, active regulation and shutdown states

- Disabled during DVID ramping

- Recommended setting is 0.4V

### OOVP Response

- Response when Vout exceeded any of the fixed or tracking OOVP threshold and when any of the OOVP enable detection is enabled

- Response time: flagged on 4 consecutive samples at a rate of 50MHz are over the threshold

### Enable detection (Fixed OUVP)

Enable/disable Fixed OUVP

Threshold detection

#### Fixed OUVP Threshold

- Output under-voltage protection

- Triggered when Vout < Fixed OUVP Threshold

- Only enabled during the active regulation state

- Recommended setting is < system required min Vout and > fixed OUVP disable threshold

#### Enable detection (Tracking OUVP)

Enable/disable tracking OUVP

Threshold detection

#### Tracking OUVP Threshold

- Triggered when (Vtarget Vout) > Tracking OUVP threshold

- Only enabled during the active regulation state

- Recommended setting is 0.3V

### OUVP Response

- Response when Vout exceeded any of the fixed or tracking OUVP threshold and when any of the OUVP enable detection is enabled

- Response time: flagged on 4 consecutive samples at a rate of 50MHz are over the threshold

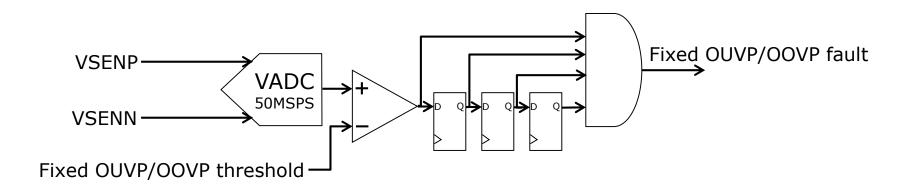

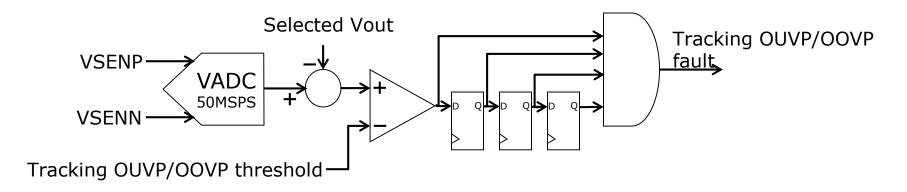

# Output Settings... Fixed/Tracking OOVP/OUVP fault

4 consecutive samples over/under the limit will trigger the fault.

# Output Settings... Vout Protection

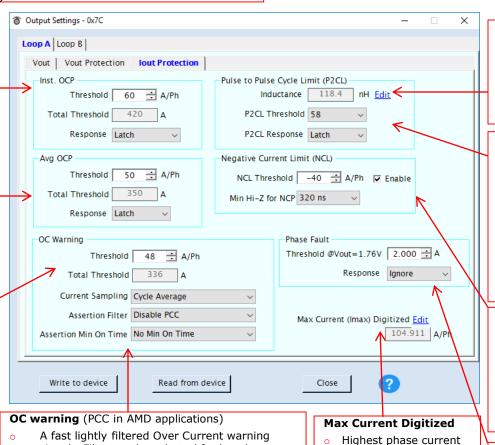

# Output Settings... Iout Protection

Note: The different thresholds for OCP and warning have an relationship and GUI may limit or round possible settings and change the other limits to match.

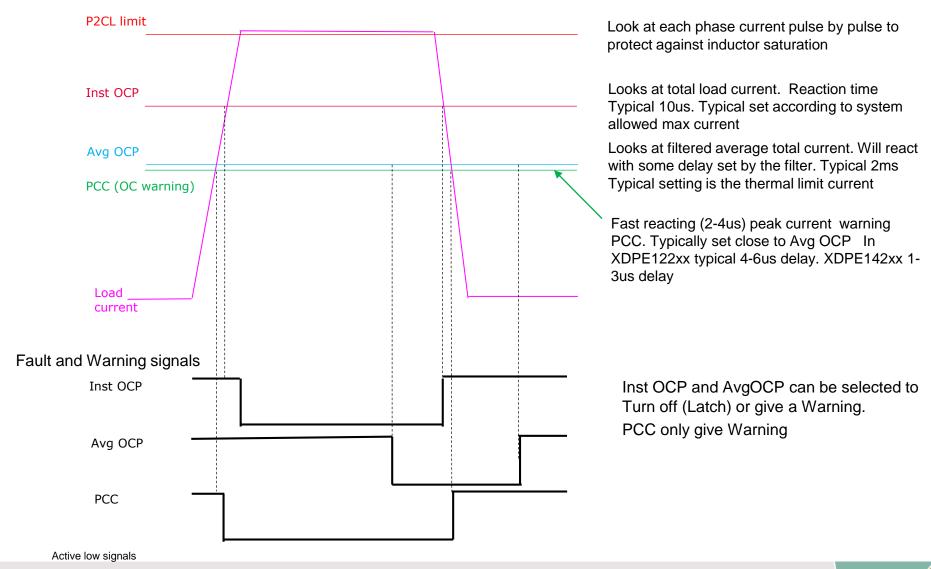

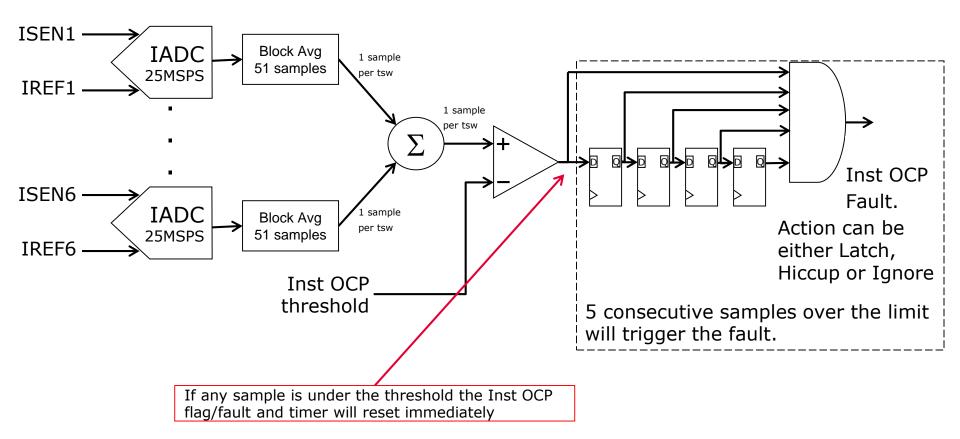

#### Inst. OCP (Over Current Protection)

- This looks at the instant peak current in each phase

- There is a 5 switching cycles delay before any action is taken

- See next page for diagram

- Response will determine what action to take when the instant peak current exceeded its limit

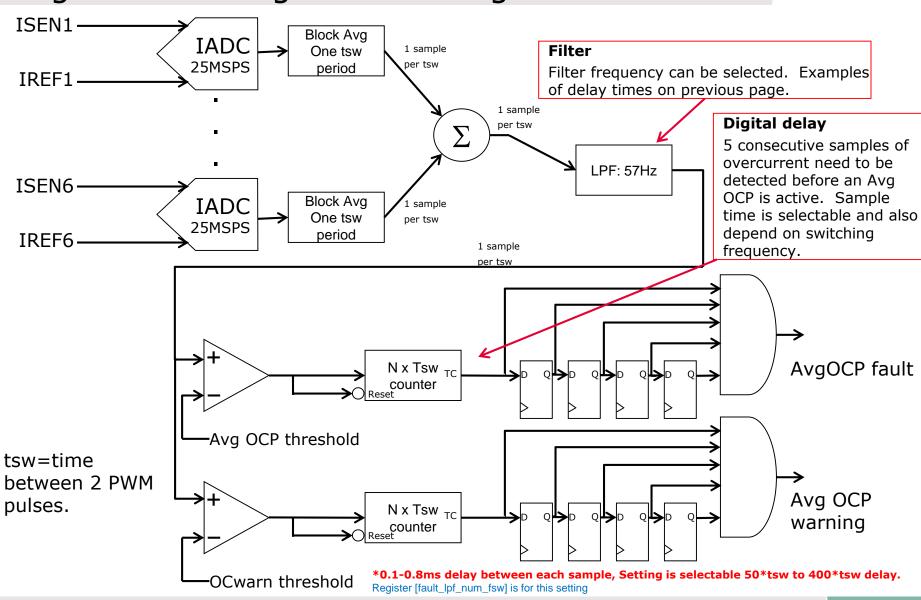

### Avg OCP (Over Current Protection)

- This looks at the average current in each phase

- Recommended settings per ph:

- Icc Max \* 1.15 / Nph Max

- Response will determine what action to take when the average current exceeded its limit

### OC Warning (Over Current)

- This looks at the average filtered current in each phase

- Fault will be triggered if the average filtered current exceeded this limit

The function Peak Current Control in Sequoia that can be selected can be set to either cycle average that is the same as Sierra or instant current which is a faster but noisier detection mode

#### **Total threshold**

Threshold that represents the total output current where the warning will be triggered

#### Inductance

- Output inductor for the buck converter that can be edited in the Feedback Loop/Output Model dialogue

- Use in the calculation for the P2CL function

#### **P2CL** (Pulse to Pulse Cycle Limit)

- Per phase current limit designed to prevent inductor saturation by monitoring peak inductor current per phase and limit PWM pulse width cycle by cycle

- Recommended value is Isat @ 125 deg C in inductor datasheet minus 1 or 2A.

- **Response** will be triggered if current exceeded this limit for 255 consecutive switch pulses

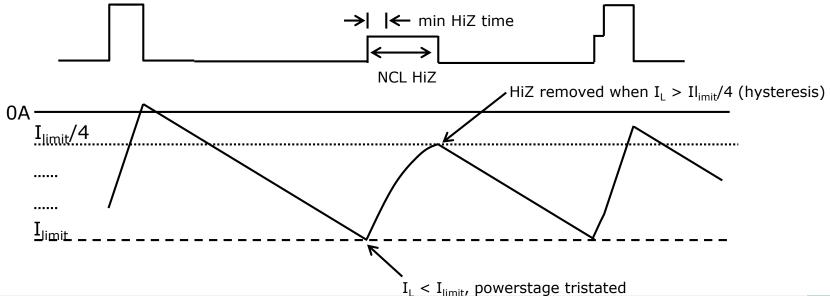

### Negative Current Limit (NCL)

- If the current in one phase goes too much negative, its PWM output will go to High Impedance (Hi-Z) for a specified minimum time.

- This function can be enabled by marking the box next to Enable.

See explanation on following pages for function

### Threshold @ vout=1.76V

Maximum difference in phase current to trigger a phase fault. It change a little depending on Vout.

### Response

Response when phase fault signal comes from power stage

that can be measured

Current Sense dialogue

Can be changed in the

signal. Filter can be selected for how long over

The output can be selected for how long it will

stay on after detection. It will reset itself after

It uses the same threshold current as set in OC

selected time if no more OC is detected.

warning.

current have to be before it activates the output.

# Output Settings... The different current limits in Sequoia/Sierra

# Output settings... Inst OCP behavior

Notice that the current measured is the inductor current and not the direct load current. Inductor current rises slower than the load current and will add a delay that depends on variables like Inductance, Input voltage, output voltage and more.

# Output Settings... NCL function explanation

- Input: Iout

- Response time: 5ns; No shutdown response available

- Recommended settings: amplitude should be greater than the negative current induced by Cdv/dt during DVID down.

- Shutdown response: Not available

- > If inductor current is too negative, highside FET may fail during the dead time between lowside off and highside on due to too much current going into the highside body diode.

- NCL will set lowside to off once the inductor current reaches the negative current limit

- To avoid chatting, the hysteresis level is set to release the HiZ only when the inductor reaches ¼ of the negative current limit and a minimum HiZ on time is satisfied.

# Output Settings... limitations in OCP settings

- There is a limitation in what values Avg OCP and OC Warning/PCC can have.

- They can be set in steps of 2A and the range is 0-30A/phase less than Inst OCP.

- When changing Inst OCP the AvgOCP and PCC will change the same amount. i.e. Change Inst OCP 7A and both other will also change 7A

- InstOCP is not influenced by changes in AvgOCP or PCC

- > Example Inst OCP = 70A / phase AvgOCP = 60A and PCC = 46A

- Change Inst OCP to 69A and that will make AvgOCP=59A and PCC=45A

# Output Settings...

# Avg OCP or Avg OC Warning behavior

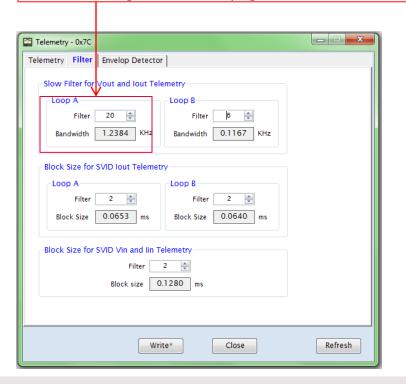

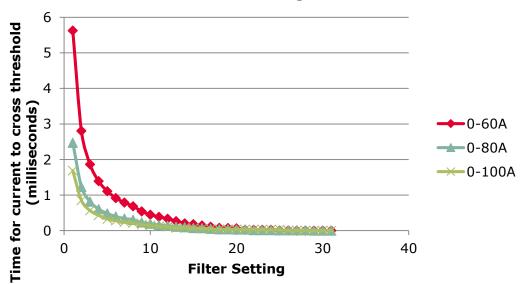

### **Filter**

Filter frequency can be selected.

Time for a overcurrent signal to pass through the filter will depend on how much overcurrent.

Like for any low pass filter a small current step take longer time to get to the threshold than a large overcurrent. See graph for example where limit is selected to 45A and different current steps.

Total delay times from an Overcurrent to fault response is the sum of Filter frequency selected and the corresponding delay time and also depend on switching frequency as there is an 5 consecutive sample digital delay after the filter. This digital delay makes higher filter frequencies insignificant to total time delay.

See block diagram on next page for more details.

# **AVG OCP Low Pass Filter Time** to cross a 45 Amp threshold

# Output Settings... Avg OCP and Avg OCP warning

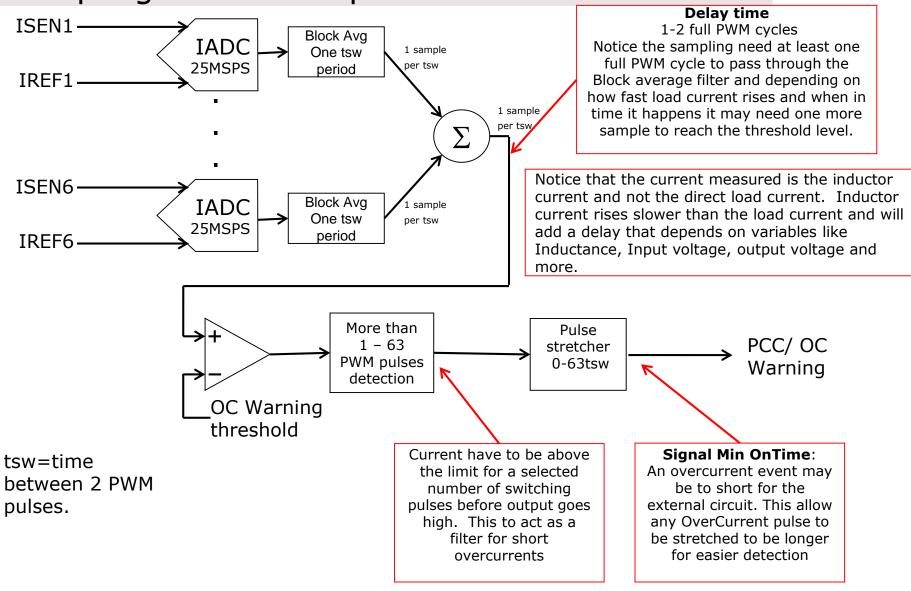

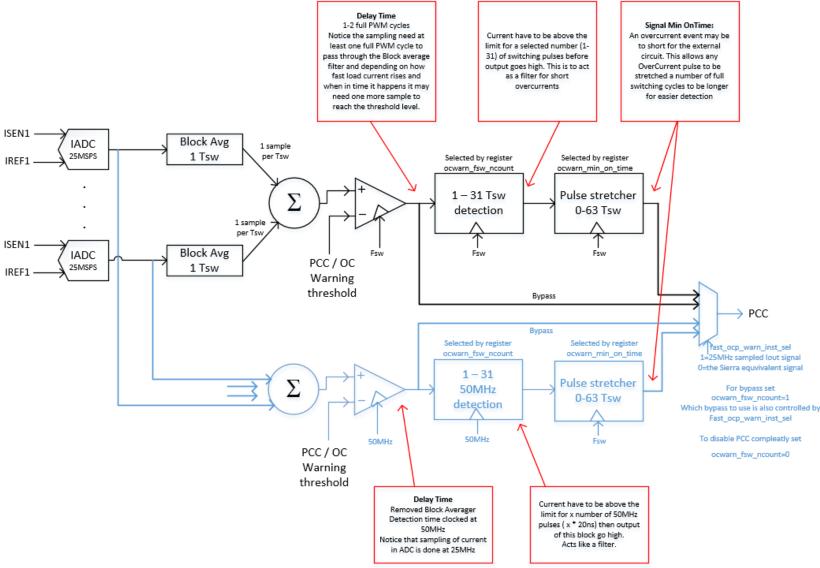

# Fast OC warning Sierra and Sequioa Cycle sampling. AMD PCC peak current control

### Fast OC warning Sequoia Inst. Current AMD PCC peak current control sampling

Symbols in Blue is the new faster PCC path added in Sequoia

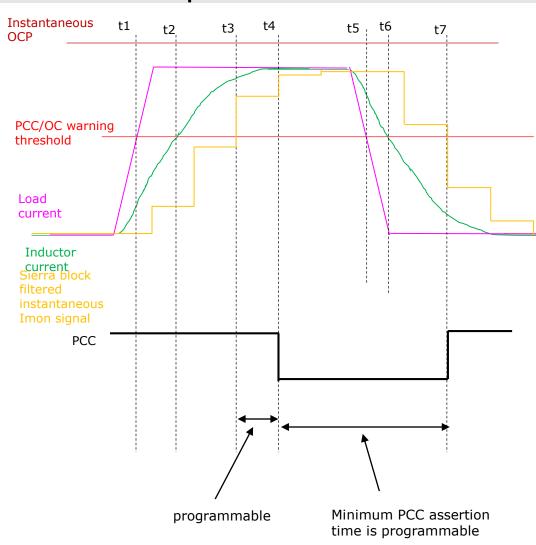

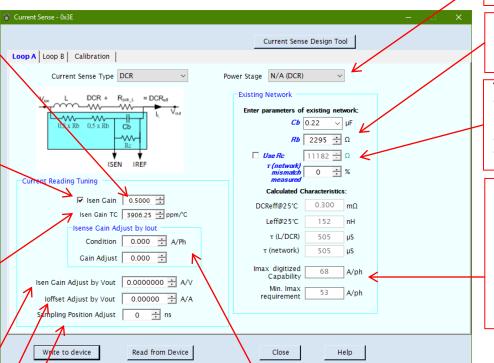

# OC warning Sierra and Sequoia AMD PCC peak current control

- t1: load current reaches OC warning threshold Some of the current comes from the output capacitors while inductor current takes time to increase

- t2: Inductor current reaches OC warning threshold. Contribution to the delay between t2 and t1:

- Output inductance (Higher=slower)

- Input voltage (higher=faster)

- Loop bandwidth ( higher=faster)

- t3: Instantaneous Imon (switching cycle block averaged inductor current) reaches OC warning threshold. Delay between t3 and t2 is <=two switching cycles

- t4: PCC is asserted. Delay between t4 to t3 is programmable in range of 1~63 switching cycles

- t5:load current decreases and reaches OC warning threshold

- t6: Inductor current decreases and reaches OC warning threshold

- t7:Instantaneous Imon follows inductor current and goes below OC warning threshold which de-assert PCC signal. Note: the assertion time should be >minimum assertion time which is programmable in range from 0~63 switching cycles

# Faster PCC only Sequoia XDPE142xx AMD PCC peak current control

t4 t5 t6

50

- Output inductance

- Input voltage

- Loop bandwidth

- t3: Current sampled at 25Mhz reaches OC warning threshold.

- t5: Inductor current decreases and reaches OC warning threshold

- t6:Current sampling follows inductor current and goes below OC warning threshold which deassert PCC signal.

PCC signal can be stretched 0-63 switch cycles Shown with 0 stretch

Copyrig ckayaho cwww.sw.band - Присоединяйся!

PCC (OC warning)

Instant current

PCC

sense fast samples

Load

current

Inductor current

t1

t2 t3

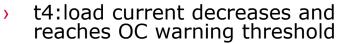

# P2CL Pulse to pulse cycle limit

Internal Calculation of phase current

Inductor value, Measured Vin, Vout and Imidpoint are used to calculate the inductor

current during the on time of the high side MOSFET.

When the calculated current reaches the P2CL limit the PWM will be truncated

# P2CL Pulse to pulse cycle limit

### Response:

- Each PWM pulse will immediately be truncated when the phase current exceed the P2CL limit

- Fault flagged after 255 switching cycles above limit.

- It uses an up/down counter.

- It will count down for all pulses that are below threshold and up again if new pulses exceed threshold.

- When number of accumulated above threshold pulses reaches 255 a fault signal is generated.

- A single pulse under threshold will not reset counter to 0 like the other current limit functions

- Counter do not go below 0

- > Recommended settings: Inductor saturation current or 1-2A below saturation current

- Shutdown response: Shutdown/Ignore/Hiccup

# Agenda

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- Nonlinear control

- 15 Current balance

- Power state transitions

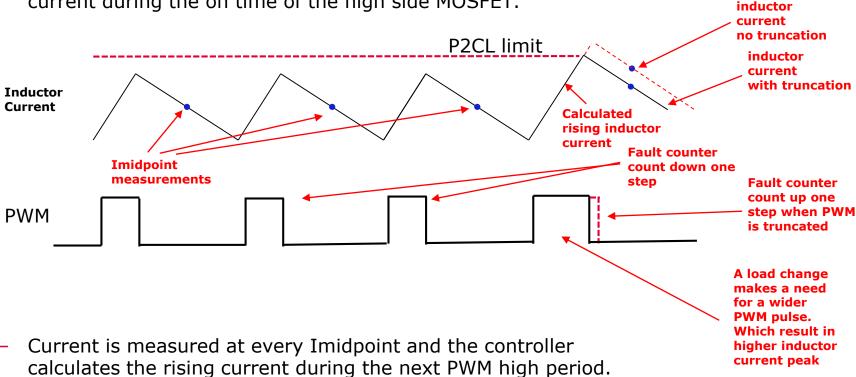

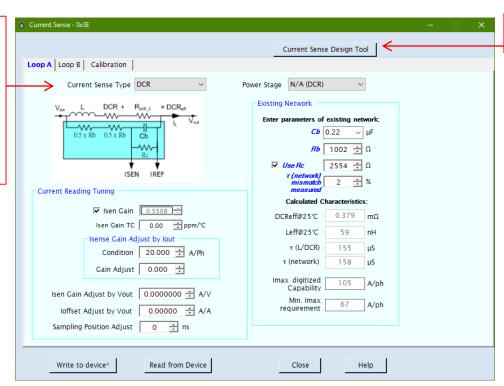

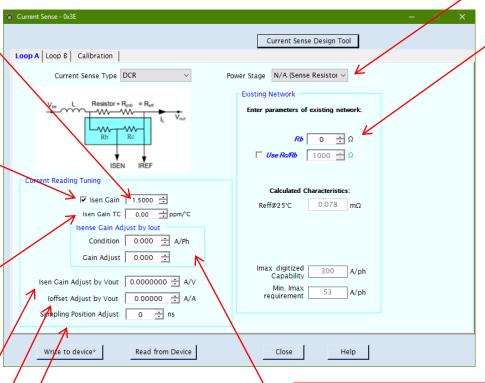

## Current sense...

### **Current Sense Type**

- For XDPE1x286 and XDPE12550 part, selection can be *DCR* sense (as shown), *DCR Shunt* or *Non-DCR* (i.e. power stage with internal current sense)

- For other parts, current sense type will automatically change to Non-DCR

- Graphical figure will change to match selection made

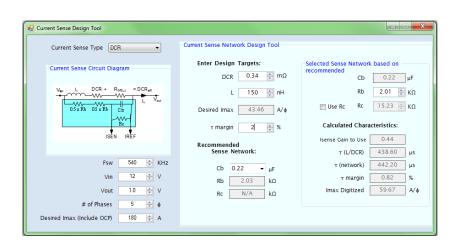

#### **Current Sense Design Tool**

Dialog that helps calculate the settings and any resistors needed

**Infineon Proprietary**

## Current sense... DCRsense

#### **Isen Gain**

- Gain factor for the measured voltage across Cb that represent the current through the inductor

- Tune this value such that the current reading gain is accurate from 0A to 2/3 of TDC with **Isen Gain TC** set at 3906.25ppm/°C when temp change in inductor is small

- To get a starting value set the gain=0.15mV/DCR

#### Isen Gain checkbox

- Checked: override calibrated gain settings from the Calibration tab

- Unchecked: gain will use values from the Calibration tab

#### **Isen Gain TC**

- Temperature Coefficient for gain

- Typically between 2000 ~ 4000 ppm/°C

- Use the ideal copper TC=3906.25 first and then based on temperature compensation result of inductor DCR to trim this value

- This value could be different by layout.

### **Isen Gain Adjust by Vout**

Linear current sense gain compensation based on Vout

### **Ioffset Adjust by Vout**

Offset f the current sense based on Vout

### **Sampling Position Adjust**

- Adjustment of reported phase current in the *Telemetry* window

- See next page for explanation

#### Power Stage

When Current sense Type is DCR, selections are DCR and Sense Resistor

#### Cb and Rb

- Enter the real values used on the PCB for capacitor and resistor

- Cb typical 0.22uF

#### T ( Network) mismatch measured

- This is the mismatch in the two time constants Rb\*Cb and L/DCR for the real components

- Typical put a value 1-2%

- Explanation follows on the next pages

## Imax Digitized and Min. Imax requirement.

- Check that the calculated Imax Digitized capability is equal or higher than Min Imax Requirement

- If not try to add more Rc to get a lower voltage on the ISEN-Iref signals. This to not exceed the 30mV input range for the current sense input for DCR.

### Isen Gain Adjust by Iout

- Optional gain adjustment to the current sense based on Iout

- Compensate for a non-linear behavior in current reporting for small currents

- For load currents greater than the specified A/ph Condition, the specified Gain Adjust value will be applied

- Recommended setting for **Condition** is 16~20A/ph

Isen Gain @  $I_x$  per phase = Isen Gain \*  $(I_x - I_{condition})$  \* (1 + GainAdjust)

# Current sense... Sense resistor

#### **Isen Gain**

- Gain factor for the measured voltage across Cb that represent the current through the inductor

- Tune this value such that the current reading gain is accurate from 0A to 2/3 of TDC with **Isen Gain TC** set at 3906.25ppm/°C when temp change in inductor is small

- To get a starting value set the gain=0.15mV/DCR

#### Isen Gain checkbox

- Checked: override calibrated gain settings from the Calibration tab

- Unchecked: gain will use values from the Calibration tab

#### Isen Gain TC

- Temperature Coefficient for gain

- Typically between 2000 ~ 4000 ppm/°C

- Use the ideal copper TC=3906.25 first and then based on temperature compensation result of inductor DCR to trim this value

- This value could be different by layout.

### Isen Gain Adjust by Vout

Linear current sense gain compensation based on Vout

### **Ioffset Adjust by Vout**

Offset f the current sense based on Vout

### **Sampling Position Adjust**

- Adjustment of reported phase current in the *Telemetry* window

- See next page for explanation

#### **Power Stage**

When Current sense Type is *DCR*, selections are *DCR* and *Sense Resistor*

With a sense resistor instead of DCR sense, the resistor divider is often 0ohm.

Typically temperature dependance TC is much less than for DCR. See resistor vendors datasheet for value.

### **Isen Gain Adjust by Iout**

- Optional gain adjustment to the current sense based on Iout

- Compensate for a non-linear behavior in current reporting for small currents

- For load currents greater than the specified A/ph Condition, the specified **Gain Adjust** value will be applied

- Recommended setting for **Condition** is 16~20A/ph

Isen Gain @  $I_x$  per phase = Isen Gain \*  $(I_x - I_{condition})$  \* (1 + GainAdjust)

# Current sense... Non-DCR

#### **Isen Gain** Turrent Sense - 0x7C Gain to use for all phases for the signal from the power stage Current Sense Design Tool Power Stage To get a starting value, set the Loop A Loop B | Calibration When **Current sense Type** is *Non*gain=0.35 when using a power DCR, select device name family Current Sense Type Non-DCR Power Stage Traveler/Voyager V stage like TDA21460 depending on the power stage Existing Network being used Isen Gain checkbox Traveler/Voyager Enter parameters of existing network Checked: override calibrated gain Bia Rock settings from the Calibration tab Sapphie/Denali REFIN Unchecked: gain will use values ► IRFE from the Calibration tab **Isen Gain Adjust by Iout** Optional gain adjustment to the current sense based on Iout **Isen Gain TC** Calculated Characteristics: ✓ Isen Gain 0.3750 ÷ Compensate for a non-linear Temperature Coefficient for gain Isen Gain TC 0.00 → ppm/°C behavior in current reporting for Typically set to 0 small currents Isense Gain Adjust by lout For load currents greater than the Isen Gain Adjust by Vout Condition 0.000 ÷ A/Ph specified A/ph Condition, the Linear current sense gain specified Gain Adjust value will Gain Adjust 0.000 lmax digitized compensation based on Vout A/ph be applied Capability Recommended setting for Min. Imax 66 A/ph loffset Adjust by Vout 0.0000000 A/V Condition is 16~20A/ph **Ioffset Adjust by Vout** Offset f the current sense based 0 💠 ns Sampling Position Adjust Isen Gain @ $I_x$ per phase on Vout = $Isen\ Gain * (I_x - I_{condition}) * (1 + GainAdjust)$ Write to device Read from Device Close a

Sampling Position Adjust

Adjustment of reported phase current in the **Telemetry** window See next page for explanation

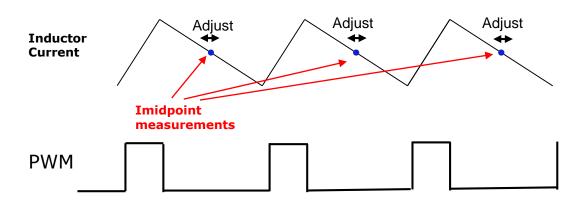

## Current Sense...

- Sampling Position Adjust. Will influence the Phase current in Telemetry window

- Current is measured at every Imidpoint of the falling edge of inductor current and the controller use this for current balance function and report the per phase current in telemetry window

- Sometimes the inductor current curve is not perfect. Delays in powerstage and distortion shift the curve and the reported phase current will not be the actual average phase current.

- This setting allow for some adjustment to get closer to the mid point of inductor current that is then reported in Telemetry window as phase current.

- Current balance is not influenced as it still compare all phases at same point in time.

With Adjust as negative the sampling occur earlier equals higher reported current Positive number delays the sampling and reports a lower phase current

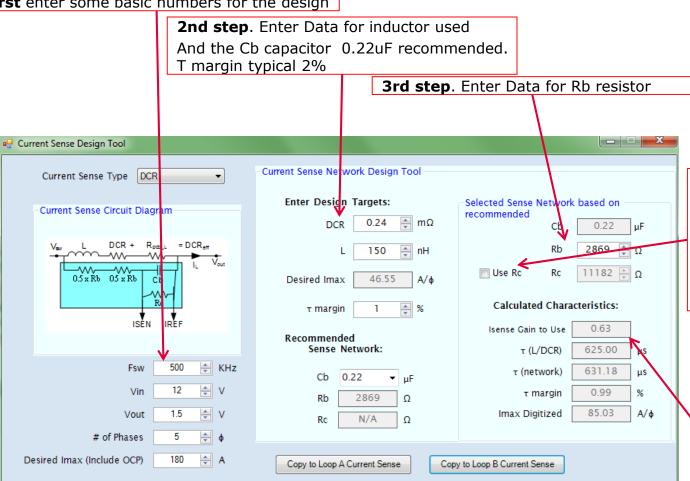

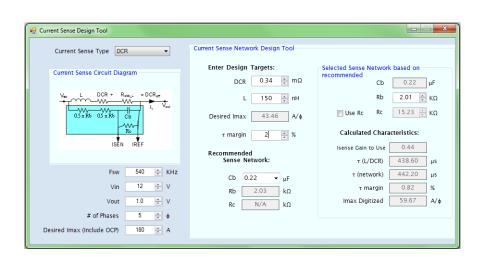

# Current sense... Current sense design tool

A tool to help calculate current sense parameters. Use knowledge from the 3 following theory slides to find suitable numbers to enter.

**First** enter some basic numbers for the design

Соругід СКАЧАНО С WWW.SW.BAND - АПРИСОЕДИНЯЙСЯ!

**Use Rc**. If there is a high DCR value the sense voltage may be needed to be divided down by using resistor Rc. If this is used mark the box and enter a number in the Rc field

**Isense gain**. Calculated value that can be used as Isense gain in the current sense window. It is to be used as starting point as final gain is determined by testina.

# Current sense... dynamic response: Rb\*Cb time constant

$$v_{Cbx} = v_{DCRx} * \frac{L/DCR}{R_b * C_b}, \quad s \to \infty$$

$$I_L$$

$$V_{DCR}$$

$$V_{Cb}$$

$$V_{Out} (w/v_{out} ($$

- Impact of how Rb\*Cb compared to L/DCReff:

- If  $R_b * C_b = L/DCReff$ ,  $v_{Cb}$  will be the same  $v_{DCR}$  at any frequency

- If  $R_b * C_b < L/DCReff$ ,  $v_{Cb}$  will underdamp  $v_{DCR}$  which leads to overshoot/undershoot during transient when LL is non-zero. To adjust time constant:

- $(R_b * C_b)_{new} = (R_b * C_b)_{orig} * (1+x/z)$

- If  $R_b * C_b > L/DCR$ ,  $v_{Cb}$  will overdamp  $v_{DCR}$ . To adjust time constant:

- $(R_b * C_b)_{new} = (R_b * C_b)_{orig} * (1-y/z)$

Current sense... Adjust DCR sense network time constant – method 1: using transient waveforms with non-zero LL slope (1 of 2)

- The DC current sense gain must be tuned before adjusting time constant → actual DCR on board DCR<sub>eff@25degC</sub> = DCR<sub>L</sub>+DCR<sub>trace</sub> can be calculated

- Step 1: enter C<sub>b</sub> and R<sub>b</sub> values used on the board

- Step 2: set up transient load from 5% TDC to 55% TDC and measure z and x or y in previous page

- Step 3: if V<sub>Cb</sub> overshoots V<sub>DCR</sub>, enter x/z to "τ mismatch measured"; otherwise, enter y/z to "τ mismatch measured"

→ actual L can be calculated

Current sense... Adjust DCR sense network time constant – method 1: using transient waveforms with non-zero LL slope (2 of 2)

- Step 5: Select the desired C<sub>b</sub> value and then R<sub>b</sub> will be calculated automatically

- Tip: recommend to keep the same C<sub>b</sub> value and only adjust R<sub>b</sub> value to minimize modifications on board

- Step 7: change the R<sub>b</sub> or C<sub>b</sub> to the new values on the board and verify DC current reading and time constants matching again

- Iteration of DC current reading and time constant adjustments might be necessary

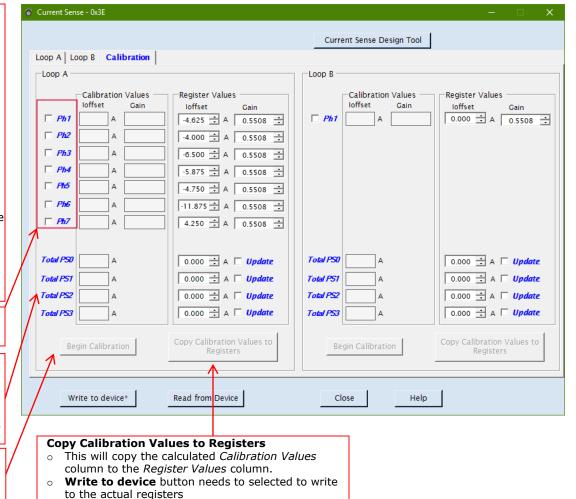

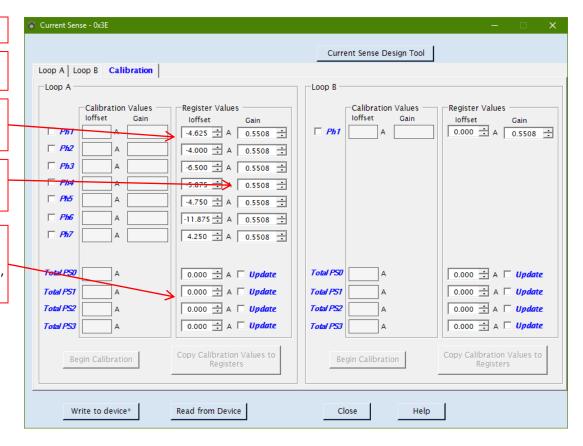

## Current sense... Calibration

- o Partly automated calibration of offset and gain per phase.

- Optimizes the reported current and compensate for variations between phases.

- It is also possible to manually enter values into the Register Value section.

#### Calibration Procedure

- Check the **Phx** checkbox to select which phase(s) to calibrate.

- 2. Click **Begin Calibration** button

- A series of pop up windows will guide the user when to turn on/off the load.

- Note: max of 30A per phase

- GUI will measure telemetry values in each phase in sequence with no load and with load and will calculate offset and gain for each selected phase.

- Calculated calibrated values will be displayed in the Calibration Values column.

- Click on the Copy Calibration Values to Registers button to copy the values to the register section.

- 4. Click the **Write to device** button to write them into memory of the controller.

#### Phx

• When checked, phase x will calculate the suggested calibration values for Ioffset and Gain.

#### Total PSx - Ioffset

- o Total loffset for each PS states.

- During calibration, calibrated values are automatically changed to 0

- Selecting the **Update** checkbox will copy these values to its equivalent Register Values dialog fields when **Copy Calibration** button is selected

#### **Begin Calibration**

- When selected, it will start the calibration process.

- Only enabled when at least 1 Phx checkbox is selected.

# Current sense... Calibration

Differences in DCR sense, power stages or layout can make each phase differ slightly in **Gain** and **Ioffset**.

Gain will be locked against changes if the "hook" on Loop A or B tab is marked as then all Gain is forced to the same setting as entered in Loop tab.

#### **Ioffset**

- Offset current for each phase.

- Can be entered manually or automated by the calibration function

#### Gain

- Gain for each phase.

- Can be entered manually or automated by the calibration function.

### **Total PSx Ioffset**

- Adjustment of reported current for different PowerStates.

- As PowerStates may use different number of phase, the reported current may change and can be compensated by adding an offset.

# Agenda

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- Nonlinear control

- 15 Current balance

- Power state transitions

# Temperature Settings

### Custom NTC design: **Shutdown response:** This button open a new window where What to do when an OTP Shutdown calculations can be done when a non temperature threshold is passed standard NTC is used \_ D X Temperature Settings - 0x3E Custom NTC Design Latch Shutdown response Loop B Loop A Temp Source Temp Source TSEN1 TSEN1 126 126 OTP Shutdown OTP Shutdown 120 ⊕ °C 120 VR HOT (Temp Alert) VR HOT (Temp Alert) TSEN1 TSEN2 Sense Method Integrated Tsens -Integrated Tsens -Sense Method Temp Offset 0.00 Temp Offset 0.00 🚔 Write to device\* Read from device Close Help TSEN1 and TSEN2:

### **Temp Source:**

Temperature signal comes from:

- -TSEN1

- -TSEN2

It is possible to have same Sensor input for both loops

### **OTP Shutdown:**

Select the temperature for when Over Temperature Shutdown is to be activated.

### VR HOT:

Select the temperature for when VR-HOT fault and pin to be activated. This function have a 3% hysteresis. i.e. When set to 100C the VR HOT warning will be set when temperature goes above 100C and stay on until temperature drops 3% (97C) then the fault flag reset itself.

### **Temp Offset:**

Allow an offset to be entered to compensate for any measurement errors or offset due to location of temperature sensor.

Copyrig CKATAHO C WWW.SW.BAND - НРИСОЕДИНЯЙСЯ!

-NTC: Use an external NTC resistor to measure temperature. Typically the NTC is placed near output inductors.

- -Integrated Tsense: Available if the power stage(s) provide an integrated temperature sense measurement

- -Disable: Do not use the temperature function

# Agenda

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- Nonlinear control

- Current balance

- Power state transitions

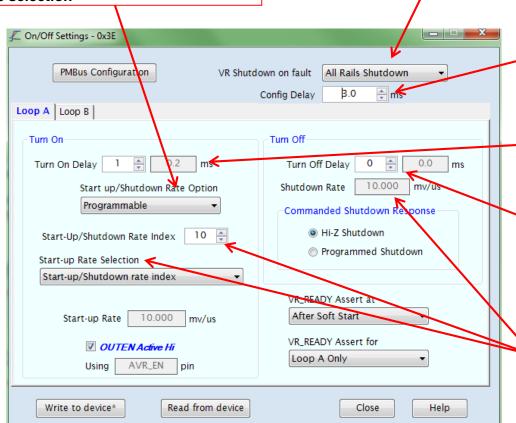

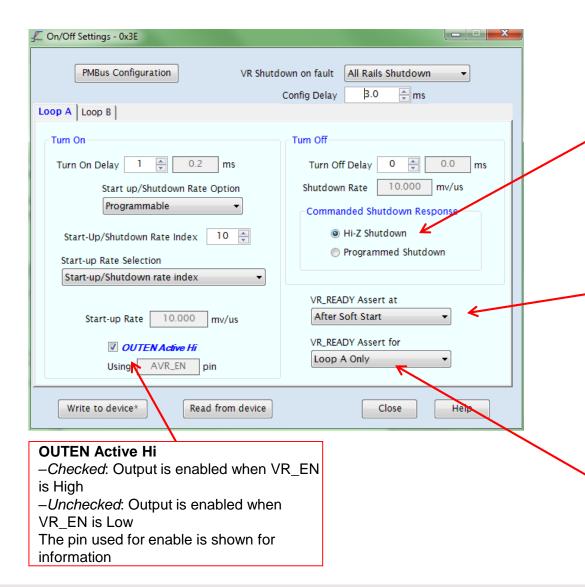

# On/Off Settings

### **Start-up Rate Option**

-Controls the rate (mV/µs) of which the controller will ramp up VOUT to the desired **Vboot** voltage or the rate for shutdown if in Programmed Shutdown mode. Start-Up and Shutdown rate can differ from each other if so selected by **Start-up/shutdown** rate selection

### **VR Shutdown on Fault**

- -All rails shutdown: all rails will shutdown due to shutdown fault

- -Fault rails only: only faulted rail(s) will shutdown due to shutdown fault

This also influence PMBus status reporting.

### **Config Delay**

-This delay is introduced after the rising 3.3Volt supply passes UVLO to ensure the voltage completely settles -After this delay, the VR will initialize the analog measurements which are sensitive to the integrity of 3.3Volt supply.

Typical set to 3.0

### **Turn On Delay**

Time from Enable signal until Vout start to ramp up.

### **Turn Off Delay**

Time from Enable signal goes away until Vout start fall.

### Start-up/shutdown rate selection

Start up ramp can be selected to be equal to or slower than the ramp for Turn off. This is useful when powering up a large capacitor bank as the slew rate can be set lower to avoid too high peak currents

The selected slew rate in mV/us for up/down is displayed for information

# On/Off Settings

Соругід СКАЧАНО С WWW.SW.BAND - АПРИСОЕДИНЯЙСЯ!

### **Commanded Shutdown Response**

-Hi-Z Shutdown: Forces both the HS and LS FETs to tri-state when the VR is turned off -Programmed Shutdown: VOUT ramps down with the rate specified in the Shutdown Rate

### **VR READY Assert at**

-After Soft Start - VR READY is asserted after the soft start ramp to VBoot is complete. This is the appropriate setting for VR13 application. -Beginning of Soft Start - VR READY is asserted after VR EN is asserted when the controller is

ready to accept SVID commands. This is the appropriate setting for IMVP8 applications

### **VR READY Asserts for**

- -Loop A only VR\_READY pin assertion for Loop A only. This is the appropriate setting where loop independent VR READY signals are needed.

- -All Active Loops VR READY pin assertion for all active loops. This is the appropriate setting where there is only one VR READY signal for multiple loops.

# On/Off Settings

# Agenda

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- Nonlinear control

- 15 Current balance

- Power state transitions

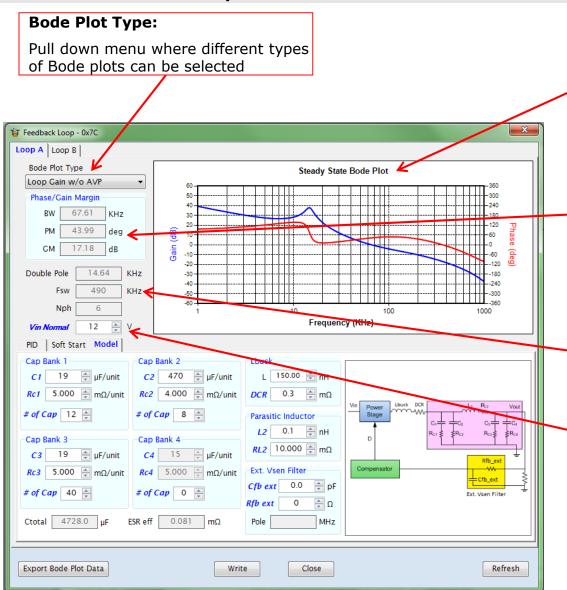

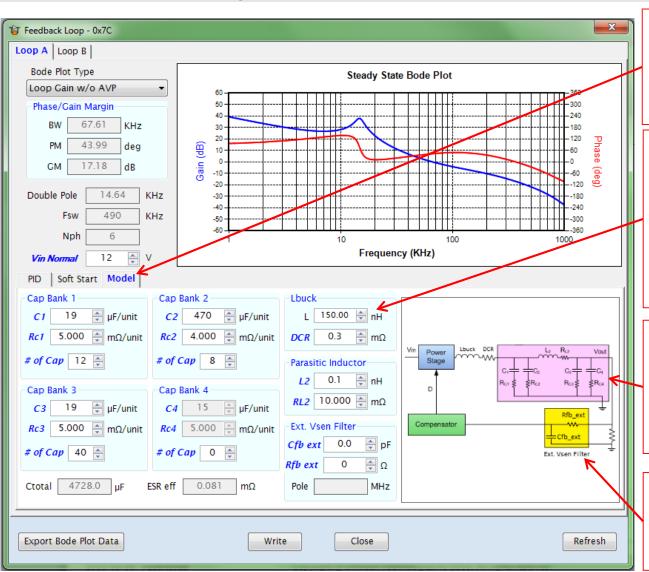

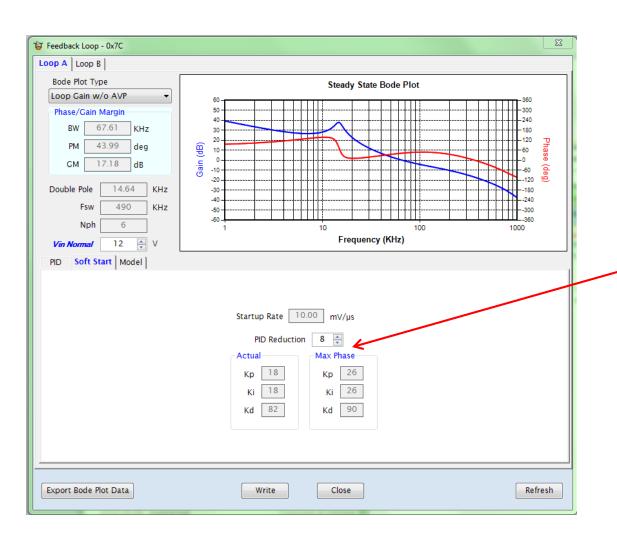

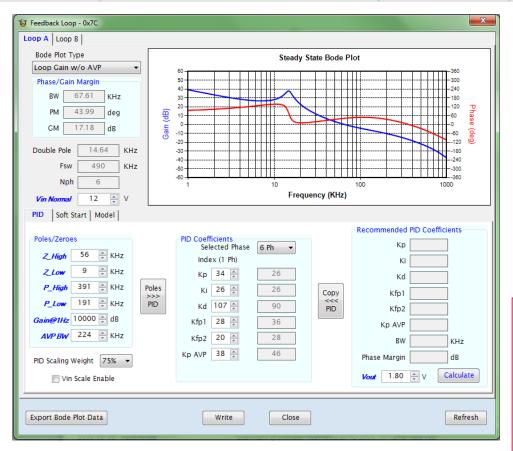

# Feedback loop

Bode plot

Shown for the condition that is selected under the **Bode Plot Type** button

**Phase / Gain Margin** is calculated based on the parameters entered in **Model** tab

BW Bandwidth. Where gain passes 0dB

PM Phase Margin

**GM** Gain Margin

For Information these parameters are shown

Double Pole: The pole due to output L

and C

**Fsw**: Switching frequency

**Nph**: Number of phases

Input voltage: Used for calculations

#### Feedback loop Model

Recommend to start with the Model tab as Bode plot depends on Model being set up with what values used.

Any derating of Ceramic capacitors due to voltage must be considered before entering Capacitor values.

#### Lbuck:

Here the Inductor value is entered. This Inductance value is saved in a register inside the controller and important to set correct for calculations to be right.

Other L and C related values on this page is used by GUI only for Bode plot and simulations. They are not saved in controller

Model simulates a CPU in a socket. Cap bank 1 and 2 are MLCC and bulk capacitors after inductors. Bank 3 and 4 are MLCC capacitors inside the socket.

Parasitic inductor L2 and R12 simulate the impedance of the copper traces into the socket

#### Ext Vsen Filter:

Simulates any resistance and capacitance in the feedback path. i.e. a 10ohm resistor that is used to inject signals for Bode measurements

## Feedback loop Soft Start

Slew rate is for information and can be selected in another place.

During softstart the PID values can be reduced to slower settings.

They do not need to be as fast responding during soft start as during normal operation.

i.e. Not the same big transients to handle.

The lower settings allow a smoother monotonic ramp of Vout

PID compensation can be optimized during soft start.

#### **Startup Rate**

- -Effective startup ramp rate

- -The startup rate can be changed in the On/Off Settings dialog

#### **PID Coefficients**

-During start up: adjust the voltage feedback loop compensation during the initial start up period only

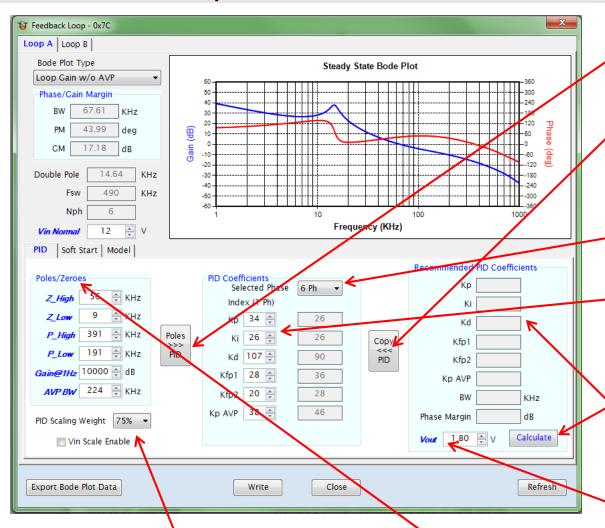

## Feedback loop PID

Poles >>> PID button

**Poles / Zeros** can be converted to **PID Coefficients** by clicking this button

Copy <<< PID button: copies Recommended PID Coefficients to the PID Coefficients

**Selected Phase:** For information the PID coefficients for different number of phases can be shown for information.

**PID Coefficients:** the coefficients can be entered directly or calculated by the GUI using the buttons.

#### **Recommended PID Coefficients**

GUI can calculate a set of recommended coefficients

Calculate button: displays the calculated PID coefficients based on the entered values in the Model tab, Vin and Vout

**Vout:** Output voltage Used for internal calculations of PID in the GUI

### PID Scaling Weight

**Vin Scale Enable** See following slides for explanation. Typical setting 75%

#### Poles / Zeros

Enter the parameters for the desired Poles and Zeros. GUI can convert this to PID coefficients

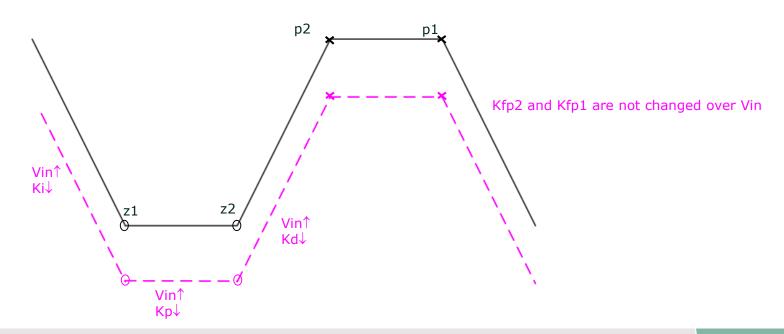

### Vin scaled PID

- Kp, Ki, Kd can be programmed to be scaled over Vin to

- Maintain the same zeros and poles location

- Keep the same gain

Note: Kfp2, Kfp1 and Kp(avp) are unchanged over Vin

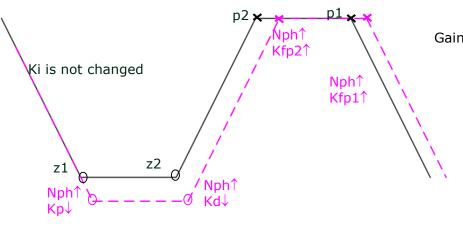

## PID scaling over Nph change (1 of 2)

Kp, Kd, Kfp2, Kfp1 and Kpavp will be scaled automatically as the Nph is being added or dropped. Note: Ki is not changed

- As Nph is increasing

- Kp, Kd is decreasing

- Kfp2, Kfp1, Kpavp is increasing

- Change of Kd is proportional to Nph and Kp, Kfp2, Kfp1 and Kpavp are proportional to square root of Nph

- z1, z2, p2, p1 are moved to the higher frequency when Nph is increasing because double pole location is moved to higher frequency

## Feedback Loop PID:

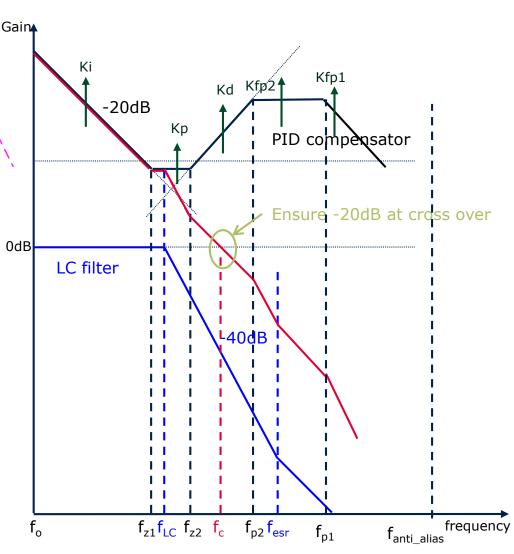

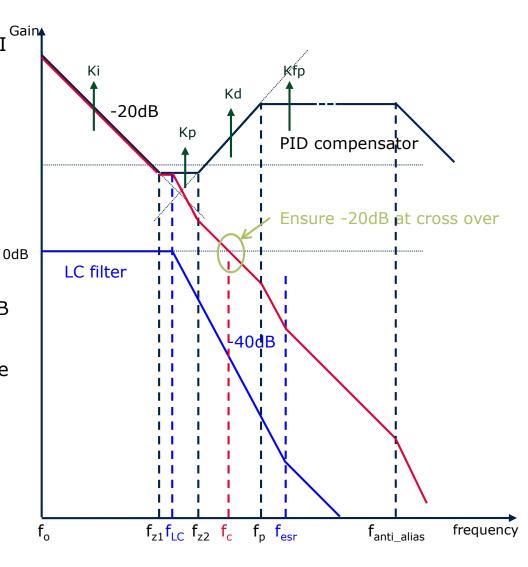

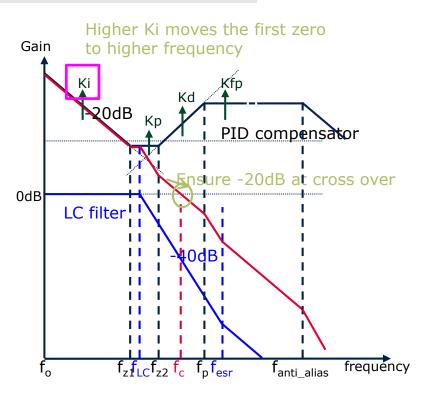

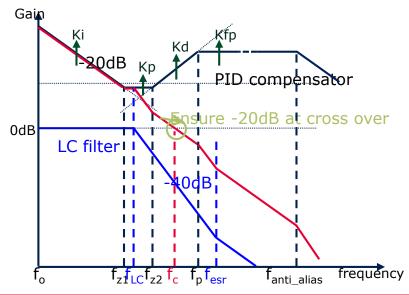

## Compensator - Steady State (Voltage Loop)

#### **PID** coefficients

- PID compensator: similar to Type III compensator

- f<sub>z1</sub>: 1st zero of PID compensator (Ki and Kp intersection)

- f<sub>z2</sub>: 2nd zero of PID compensator (Kp and Kd intersection)

- f<sub>o</sub>: pole at origin (Ki)

- f<sub>p</sub>: high frequency pole (Kd and Kfp intersection)

- f<sub>anti\_alias</sub>: high frequency anti-alias pole @ around 10MHz for LoopA/B

- LC filter:

- o f<sub>LC</sub>: output LC filter double pole

- f<sub>esr</sub>: ESR zero of C<sub>out</sub>

## Feedback Loop PID: Recommendations for Designing a Stable Voltage Feedback Loop

- The first zero should be placed on the left side of the LC filter's double poles, and the second zero placed on the right side of the double poles

- The cross-over frequency (fc) or bandwidth (BW) should not exceed 1/4 of the switching frequency

- The Gain should cross the 0dB threshold with a slope of -20dB /dec

- **Kp/Ki/Kd/Kfp** values are larger for lower phase-count than that for higher phase-count >

- PID coefficients are non-linear. Coefficient index delta of 32 is equivalent to 6dB change in gain

- **Kp(AVP)** should be smaller for VR's where a large DC load-line setting is required

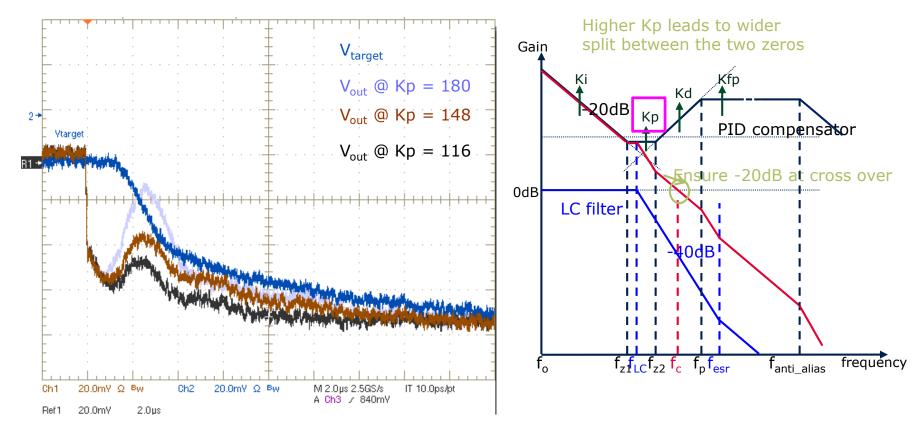

# Feedback Loop PID: Steady State Voltage Loop Compensation Kp impact on transient

- P term is proportional to Verr. The higher the Kp the higher the BW, but the higher the ring back

- From the time domain transient response:

- Kp mainly affects the first ring back amplitude

- Kp has some impact on first undershoot beyond 100ns of load stepping

**Note: Kp** affects the transient response within the first 5us

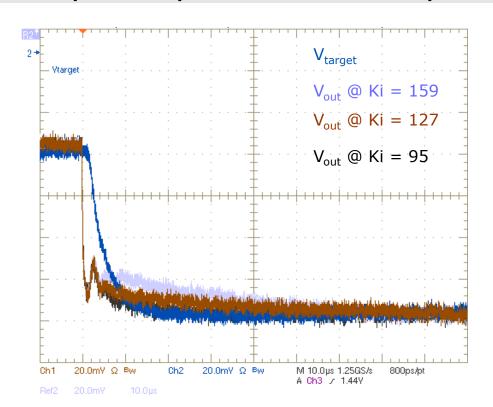

## Feedback Loop PID: Steady State Voltage Loop Compensation Ki impact on transient

- I is the integral term used to drive the DC value of Verr to zero

- From the time domain transient response, **Ki** mainly affects:

- The settling trend of V<sub>OUT</sub> after the initial transient response

- If Ki is too high, V<sub>OUT</sub> overshoots V<sub>target</sub> in the highlighted region

- If **Ki** is too low,  $V_{OUT}$  may lag  $V_{target}$  in the highlighted region can cause extra undershoot

**Note:** Ki affects the transient response after the initial 10us to 40us

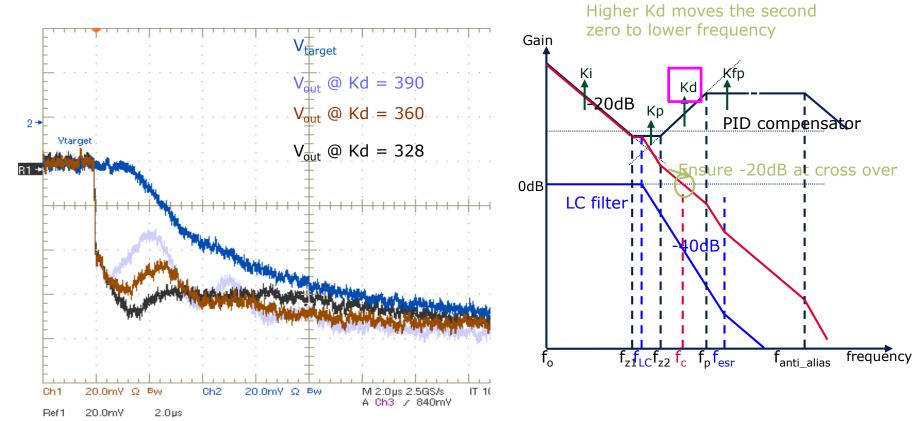

# Feedback Loop PID: Steady State Voltage Loop Compensation Kd impact on transient

- D is the derivative term. The higher the Kd, the higher the BW but with less phase margin

- From the time domain transient response, Kd mainly affects:

- The first undershoot beyond the 100ns of load stepping. The higher the Kd, the less the undershoot

- But too high of Kd will cause V<sub>OUT</sub> ringing due to insufficient phase margin

**Note: Kd** affects the transient response within the first 5us

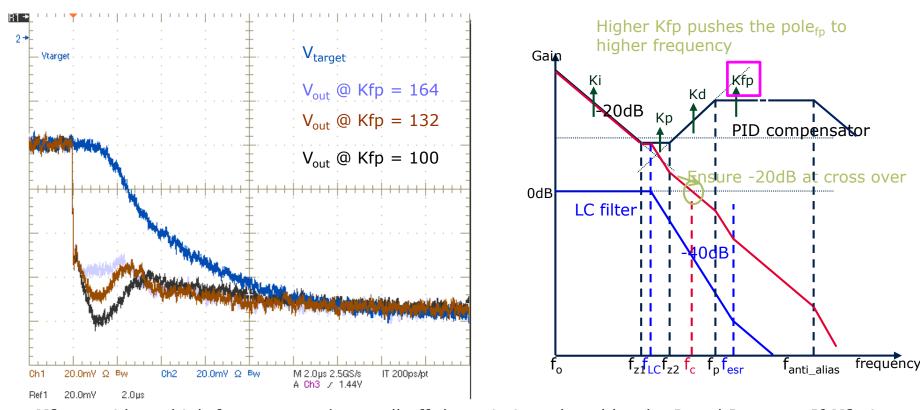

## Feedback Loop PID: Steady State Voltage Loop Compensation Kfp impact on transient

- **Kfp** provides a high frequency pole to roll off the gain introduced by the P and D terms. If **Kfp** is too high, the D term gain at high frequency will not be attenuated and hence results in less phase margin

- > From the time domain transient response, **Kfp** mainly affects:

- The first undershoot beyond the 100ns of load stepping. The higher the Kfp, the less the undershoot

- But if Kfp is too high it will lead to V<sub>OUT</sub> ringing due to insufficient phase margin

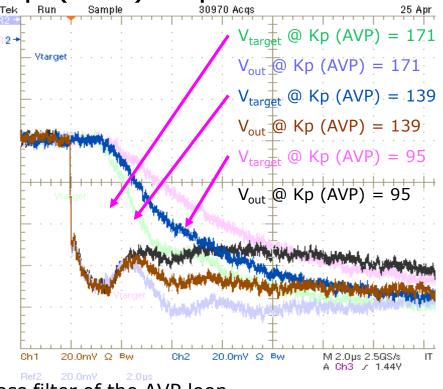

# Feedback Loop PID: Steady State Voltage Loop Compensation Kp (AVP) impact on transient

- Kp(AVP) is the low pass filter of the AVP loop.

- From the time domain transient response, Kp(AVP) mainly affects:

- how fast the target voltage can track the changing inductor current during transient conditions

- If Kp(AVP) is too low, V<sub>OUT</sub> will take longer to settle to the final DC target

- The higher the  $\mathbf{Kp(AVP)}$ , the higher the AVP loop BW, and it may overlap with the voltage loop to induce extra undershoot or ringing at  $V_{\text{OUT}}$

**Note: Kp(AVP)** affects the transient response in 5us to 20us

**Infineon Proprietary**

## Feedback Loop PID:

## Infineon

## Compensator - Steady State (Voltage Loop)

#### Poles/Zeroes

- Z1: first zero at f<sub>Z1</sub>

- Z2: Second zero at f<sub>Z2</sub>

- P\_Low: pole at fp

- P\_High: pole at f<sub>anti\_alias</sub>

- Gain @ 1Hz: DC gain

- AVP BW: AVP bandwidth

- Poles>>>PID button: calculates and populates the desired PID coefficients based on Poles and Zeros information entered

## Agenda

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- 14 Nonlinear control

- Current balance

- Power state transitions

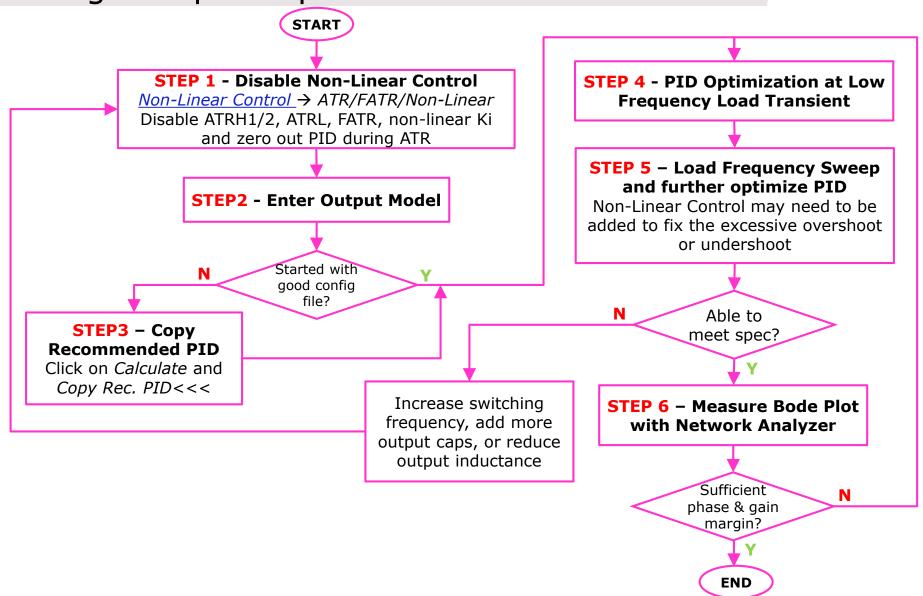

## Voltage Loop Compensation Procedure

## Agenda

- 9 Current sense

- 10 Temperature

- 11 On/off settings

- 12 Feedback loop

- 13 Voltage loop compensation procedure

- 14 Nonlinear control

- 15 Current balance

- Power state transitions

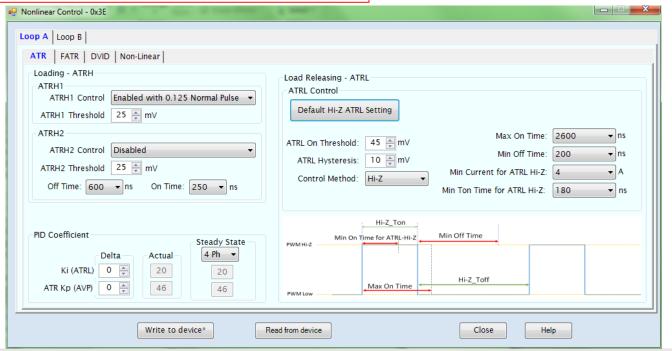

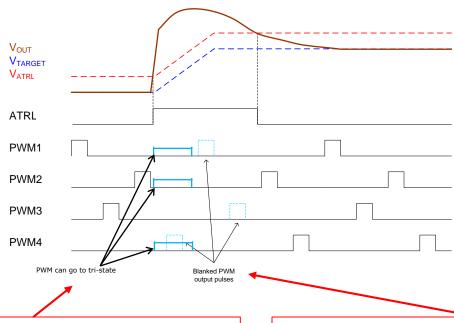

The following parameters can be programmed in the **Nonlinear Control** dialog:

- Active Transient Response (ATR) parameters to reduce undershoot or overshoot excursions during transient load events

- Frequency Active Transient Response (FATR) parameters to improve transient response over output load frequency, especially for transient loads at beat frequency

- Dynamic VID (DVID) parameters to optimize the VR's response to the SetVID\_Fast/Slow/Decay commands

- Non-Linear parameters to gain more undershoot or overshoot margin at high load repetition frequency

- Feed forward parameters to gain faster response during the specific cases listed below or variable case as below

## Only enable the ATR functions if adjusting PID alone can not meet the undershoot and overshoot requirements

- -ATR control mechanisms are driven by comparators and programmable thresholds

- -The response is non-linear and may add jitter at the output

- The thresholds should be at least 5mV (typically 10mV) wider than the measured steady state ripple voltage

- If ATR has to be enable, the PID should be made less aggressive □ start by adjusting(lower) Kd and Kfp terms

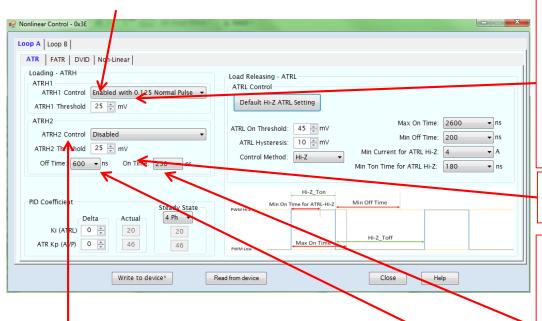

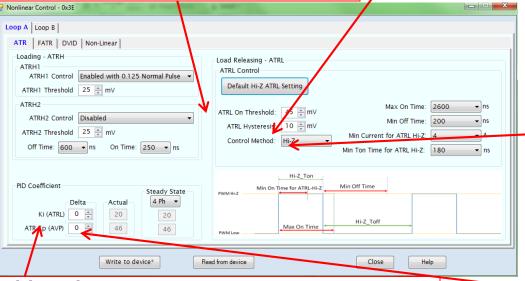

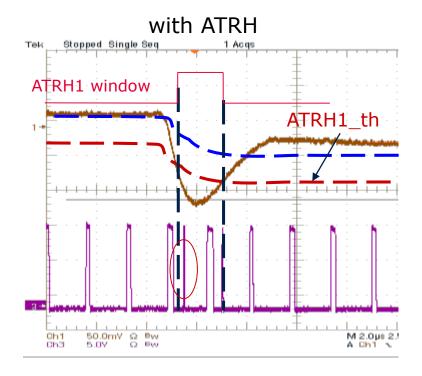

#### **ATRH1 Control**

- -Use to program the strength of the ATRH1 control

- -A wider pulse width corresponds to a stronger ATRH1 control

- -Disable: No ATRH1 control

- -Enabled with 0.50/0.375/0.25/0.125 Normal Pulse: ATRH1 control is enabled. The normal pulse width is decided by the feedback loop control and ATRH1 will be fired in 0.50/0.375/0.25/0.125 normal pulse width

- -Recommended starting point is 0.25 of normal pulse if ATRH1 is needed. Stronger ATRH control reduces the undershoot of VOUT but will increase ring-back.

## ATRH2 Control . Only use if ATRH1 is not enough.

- -Disabled: no ATRH2 control,

- Enabled with Pulse Control: ATRH2 pulse width is programmed by the Off Time and On Time

#### **Off Time**

-Off time (PWM low duration) of the ATRH2 pulse when ATRH2 Control is set to Enabled with Pulse Control

#### **ATRH1 Threshold**

- -ATRH1 control threshold

- -The smaller the threshold, the stronger the ATRH1 response because of the increased likelihood that ATRH1 will be triggered

- -It is recommended that the threshold not be too close to the steady-state ripple size, otherwise ATRH pulses can be falsely fired during normal regulation. Select a threshold at least 10mV higher than measured VOUT switching ripple.

#### ATRH2 Threshold-ATRH2 control threshold

- -Similar to ATRH1 Threshold

- Recommended to set > ATRH1 Threshold

#### **On Time**

- -On time (PWM high duration) of the ATRH2 pulse when ATRH2 Control is set to Enabled with Pulse Control

- -If ATRH2 On time is too narrow, it could be swallowed by the driver and then provide little or no help in reducing undershoot

- -If ATRH2 On time is too large, it could saturate output inductor. It can also make the PWM width too wide and be limited by the maximum duty cycle setting.

- -Select ATRH2 pulse in the range of 100ns to 200ns and select a much longer Off time (>800ns) for robust ATRH2 behavior

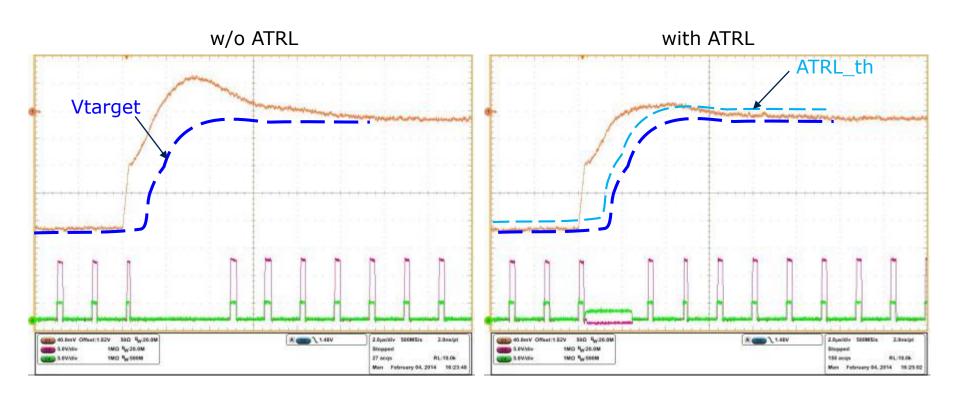

#### **ATRL On Threshold**

-ATRL will be engaged if the VOUT overshoot exceeds the target VOUT plus this threshold -Recommended not to set smaller than the switching ripple amplitude, otherwise it will be

falsely fired in the steady state

#### **ATRL On Hysteresis**

-Prevents ATRL window chattering and hence stressing FET drivers-Recommended value is 10mV

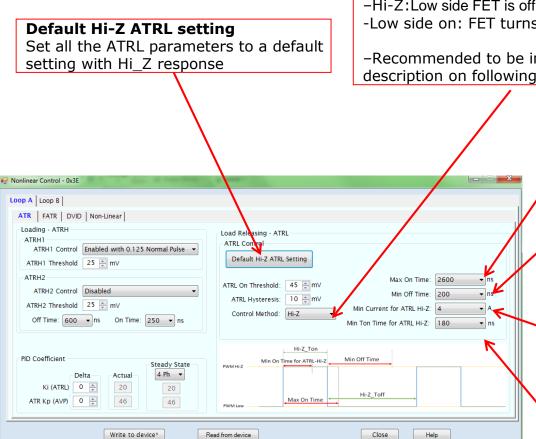

#### **Control Method**

- -Disabled: Disable ATRL

- -Hi-Z: Low side FET is off, uses Body diode

- Low side on: FET turns on when ATRL

window is active

- Recommended to be in Hi-Z if ATRL needs to be enabled

- •When both high side FET and low side FET are off, the positive current will go through the low side body diode

- •Compared to the path through low side FET, the low side body diode will cause a larger voltage drop across the low side FET and be able to reduce the positive inductor current sooner, thereby more effectively reduce the overshoot

#### Ki (ATRL)

- -Delta: This will reduce Ki when the ATRL window is active regardless of ATRL function is enabled/disabled. When the ATRL window is active, less error Voltage signal will be accumulated by the integrator which allows the average VOUT to be shifted up during high frequency transients that relieves some stress on meeting the undershoot specifications.

- -Actual: Calculated value based on the Delta and Steady State

- -Steady State: Steady state Ki value for different number of phases

#### ATR Kp (AVP)\*

- -Delta: Kp(avp) index when ATR is detected

- -Actual: Calculated value based on the

Delta and Steady State

-Steady State: Steady state Kp value

for different number of phases

#### **Control Method**

Copyrig CKAYAHO C WWW.SW.BAND - ATTPHEOEDINHANCA!

- -Disabled: Disable ATRL

- -Hi-Z:Low side FET is off, uses Body diode

- -Low side on: FET turns on when ATRL is active

- -Recommended to be in Hi-Z if ATRL needs to be enabled. See description on following slides

#### **Max Off Time**

-Maximum PWM Hi-Z duration in ATRL Hi-Z control mode when the ATRL window is active

#### **Min Off Time**

-Minimum PWM low duration in ATRL Hi-Z control mode when the ATRL window is active

#### Min Current for ATRL Hi-Z

-Minimum current in ATRL Hi-Z control mode when the ATRL window is active. If the current (per phase) is lower the setting here, the ATRL control mode will become "Low Side ON" See next page for more details

#### Min Ton Time for ATRL Hi-Z

-Minimum PWM Hi-Z duration in ATRL Hi-Z control mode when the ATRL window is active

#### Min Current for ATRL Hi-Z

- -When the phase current is lower than the setting specified here, the ATRL behavior will be changed from Hi-Z to LSFET on

- -Minimum positive inductor required to sustain Hi-Z state during ATRL

- -When the inductor current falls below this threshold, the low side FET will turn on to continuously discharge the output cap

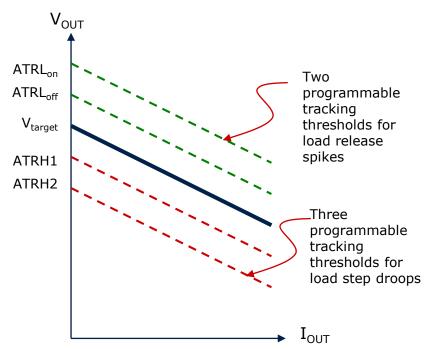

# Nonlinear Control: ATR Overview

- Active Transient Response (ATR) is used to reduce undershoot or overshoot excursions during transient load events

- ATRH: Actively inserts additional pulses (PWM High pulses) on each phase to minimize undershoot during load step conditions

- ATRL: Actively turns on the low side FET(s) (PWM Low pulses) or forces PWM into tri-state so that the inductor current can go through the low side body diode during load release conditions

ATRH threshold: ATRH will be fired when the droop caused by the load step is above the programmed threshold

- ATRH1/2 programmable thresholds

- ATRL threshold: ATRL will be fired when either of the 2 programmable tracking thresholds are entered during load release spikes

- ATRLon

- ATRLoff = ATRLon Hysteresis

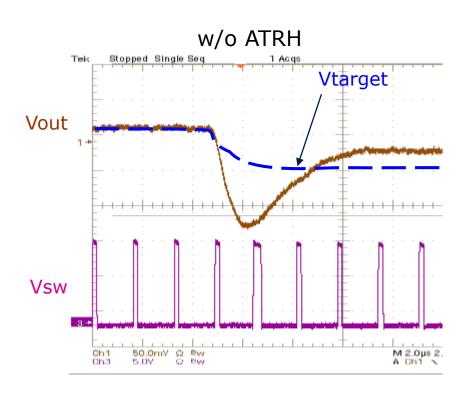

## Nonlinear Control: ATRH

- ATRH undershoot detector

- Use during positive load steps to enable the additional PWM pulses on top of the regular scheduled PWM pulses controlled by the PID

- This adds pulses to one or more phases to reduce the V<sub>OUT</sub> undershoot

- When V<sub>OUT</sub> is below the ATRH threshold, the corresponding ATRH window will be activated

- The firing of ATRH pulses between phases are "scheduled" to prevent inductor saturation

- The pulse width of the ATRH pulses is controlled by a combination of the PID and the programmable on/off time durations

# Nonlinear Control: ATRH

- When the load undergoes a positive step (increased load current), V<sub>OUT</sub> droops

- > When V<sub>OUT</sub> < ATRH\_th, the controller will fire extra PWM pulses to reduce undershoot

Copyrig CKAYAHO C WWW.SW.BAND - НРИСОЕДИНЯЙСЯ!

The ATRH\_th is equal to target voltage minus ATRH threshold

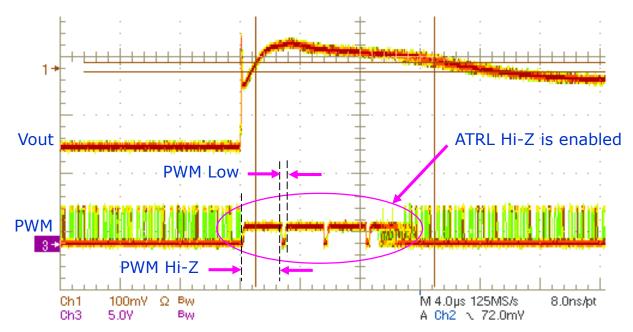

## Nonlinear Control: ATRL

- ATRL overshoot detector

- Use during negative load step (load current release) to quickly bring the PWM outputs to a Hi-Z or Low state (depending on what the programmed action is)

- This turns off the power stage in Hi-Z mode letting current flow through the Body diode to dissipate the energy.

- Or when in Low Side On mode turns on the low side FET

to reduce the V<sub>OUT</sub> overshoot

- When  $V_{OUT}$  is above the ATRLon threshold, the ATRL window will be activated and deactivates once  $V_{OUT}$  drops below ATRLoff threshold.

- If ATRL is disabled normal switching will continue and the PWM pulses will be shorter during the load release compared to when ATRL is on and either PWM pulses are supressed (LowSide FET on) or High Impedance (Hi-Z) to force current through the FET body diode.

## Nonlinear Control: ATRL

- When the load is released, V<sub>OUT</sub> overshoots due to excess energy in the inductor being transferred to the output capacitors

- When V<sub>OUT</sub> > ATRL\_th, activating a PWM Hi-Z or Low Side On mode will attempt to dissipate some excess energy to reduce overshoot

- ATRL\_th is target voltage plus ATRL on threshold

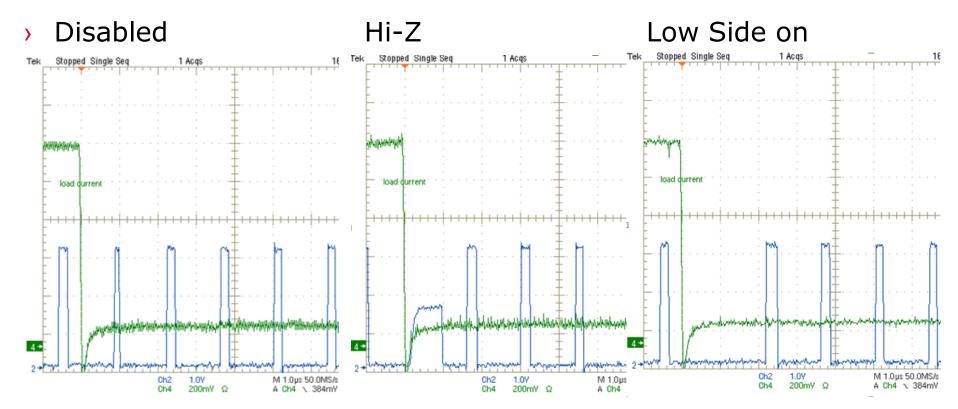

## Nonlinear Control: ATRL

The three settings for ARTL will treat the PWM signal differently

Disabled=ATRL is not active at all. PWM pulses continue

Hi-Z= Let the circulating current go through the body diode of the bottom FET

Low Side On= FET is on and let inductor current circulate through bottom FET and pulses are skipped.

# Nonlinear Control: ATRL

#### Hi-Z

All PWM phases tri-state at the same time to all phases until Vout falls below ATRL threshold voltage

#### Low Side on

PWM pulses are blanked the whole time Vout is above ATRL threshold voltage

#### **Disabled**

PWM pulses are continuing during the load release.

PWM pulses may be blanked for high Vout overshoot depending on how fast PID regulation reacts

100

## Nonlinear Control: ATR Recommendations

- Only enable the ATR functions if adjusting PID alone can not meet the undershoot and overshoot requirements

- ATR control mechanisms are driven by comparators and programmable thresholds

- The response is non-linear and may add jitter at the output

- The thresholds should be at least 5mV (typically 10mV) wider than the measured steady state ripple voltage

- If ATR has to be enable, the PID should be made less aggressive → start by adjusting Kd and Kfp terms

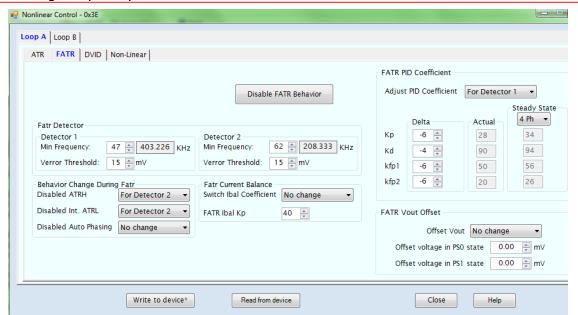

- >FATR can improve transient response over output load frequency, especially for transient loads at beat frequency.

- >FATR is made up of 3 independent load frequency detectors and adjustment controls that activate when the target load frequencies are detected.

- >Only enable FATR if adjusting PID and ATR together still cannot meet the undershoot and overshoot requirements.

- >Recommended FATR settings are the default settings when FATR is required.

- >Recommended FATR settings for manual optimization of the FATR settings

- -Step 1: Determine the oscillation frequency

- -Step 2: Determine the cause of the oscillation

- •If it is due to ATR, disable ATR at a frequency that is slightly below the frequency determined in step 1

- •If it is due to an aggressive PID, lower the bandwidth at a frequency that is slightly below the frequency determined in step 1

- •If it is due to current balance, increase the current balance Kp coefficient at frequencies above one-fifth of the switching frequency

**Infineon Proprietary**

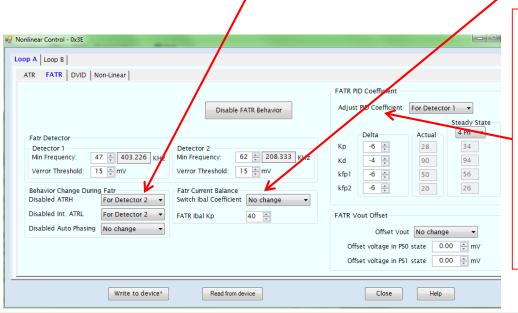

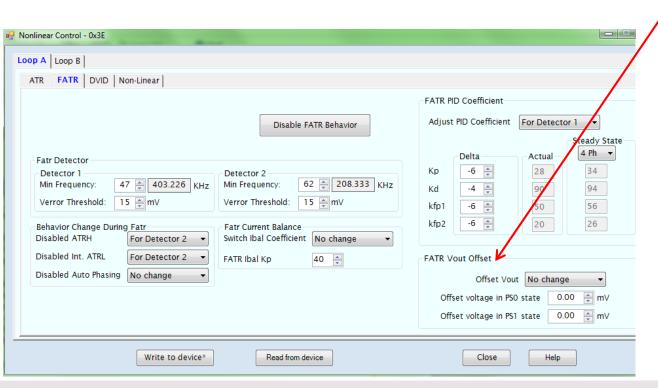

## **Disable FATR Behavior / Restore FATR Behavior**

Button will toggle the text each time it is clicked

-Selection boxes below will display "No Change" in terms of FATR behavior when disabled

#### Min. Freq. (Detector 1 and 2)

- –Minimum load transient frequency for Detector 1 and 2  $\,$

- -A frequency above the specified frequency and an amplitude above Verror Threshold will execute FATR settings.

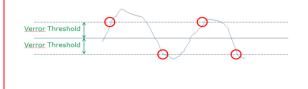

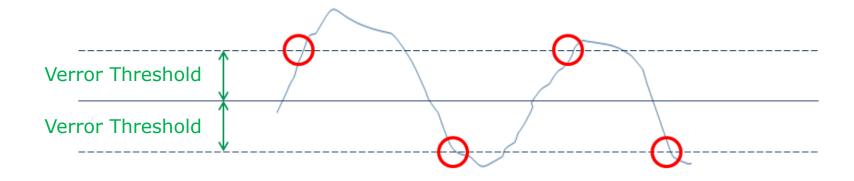

#### **Verror Threshold (Detector 1 and 2)**

- -Defines the window which the controller counts the number of crossings above and below the Verror threshold over time to determine the load repetition frequency

- -Verror threshold should be greater than the output ripple voltage to avoid false detection.

#### Nonlinear Control - 0x3E Loop A Loop B ATR FATR DVID Non-Linear FATR PID Coefficie PID Coefficient For Detector 1 Disable FATR Behavior Steady State 4 Ph ▼ Actual Delta Fatr Detector 28 34 Detector 1 Detector 2 Min Frequency 47 🚔 403.226 KHz 62 🚔 208.333 KHz 90 94 15 🚔 mV 15 🚔 mV Verror Threshold: -6 💠 56 kfp1 50 -6 💠 26 kfp2 Behavior Change During Fatr Fatr Current Balance Switch Ibal Coefficient No change Disabled ATRH For Detector 2 Disabled Int. ATRL For Detector 2 40 🚔 EATR Vout Offset FATR Ibal Kp Disabled Auto Phasing No change Offset vout No change Offset voltage in PSO state 0.00 🖨 mV Offset voltage in PS1 state Write to device\* Read from device Close

#### **FATR Current Balance**

-The recommended setting is to adjust the current balance parameter Kp (**FATR Ibal. Kp**) to ≥40 at and above one-fifth of the switching frequency to mitigate circulating current

**Behavior Change During FATR**: select the desired behavior for various Non-Linear features when the load frequency is above the FATR setting

- -No Change: no behavior change

- -For Detector 1 or 2: behavior change based on the detector value selected

#### **FATR Current Balance**

-The recommended setting is to adjust the current balance parameter Kp (**FATR Ibal. Kp**) to ≥40 at and above one-fifth of the switching frequency to mitigate circulating current

#### **FATR PID Coefficient**

-Reducing the PID coefficients during load transient will help stabilize the system

#### -Adjust PID Coefficient

- •adjust PID coefficient based on the detector selected

- -Kp/Kd/Kfp

- •Delta: allows user to set PID coefficient changes

- •Actual: Calculated value based on the Delta and Steady State

- •Steady State: Steady state values for the 1Ph, 2Ph, or MaxPh

#### **FATR Vout offset**

Allows offset compensation that in some conditions can occur when FATR is active

## Nonlinear Control: FATR

#### **Verror Threshold (Detector 1/2)**

- Defines the window which the controller counts the number of crossings above and below the Verror threshold over time to determine the load repetition frequency

- Verror threshold should be greater than the output ripple voltage to avoid false detection

## Nonlinear Control: FATR

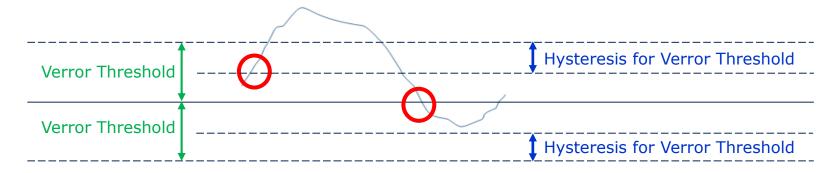

#### **Hysteresis for Verror Threshold**

Once the load repetition frequency has been detected, the hysteresis threshold reduces the threshold necessary to stay at the detected frequency

**Behavior Change During FATR**: select the desired behavior for various Non-Linear features when the load frequency is above the FATR setting

- No Change: no behavior change

- For Detector 1/2/3: behavior change based on the detector value selected

- ATRH Disabled Rate

- Rate that applies to both entering and exiting the behavior

- Recommended settings is Slew

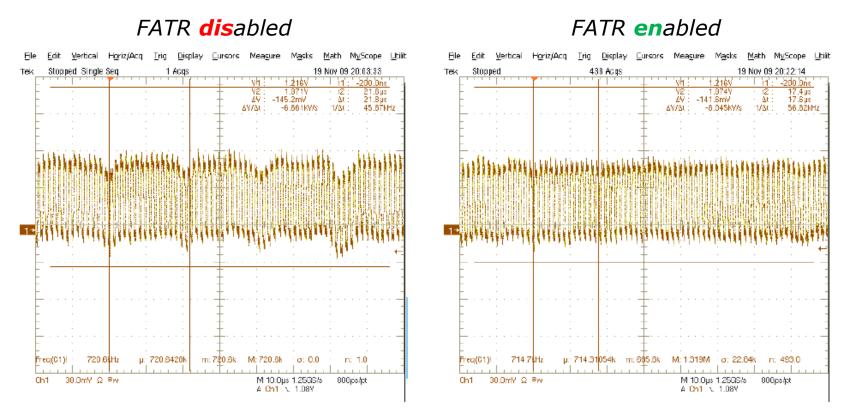

# Nonlinear Control: FATR Design Example

- Observation: V<sub>OUT</sub> oscillation at load frequencies above 700kHz

- Optimization: Reduce PID in FATR PID Coefficient for load frequencies > 700kHz

### **VOUT Waveform Comparison**

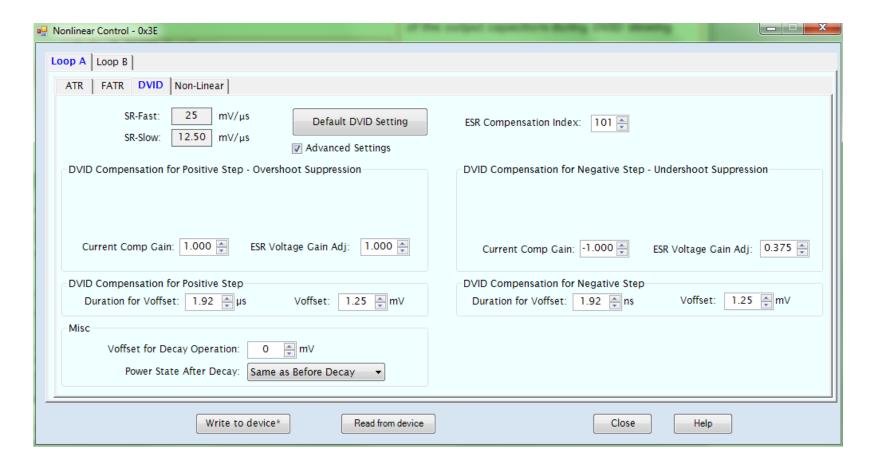

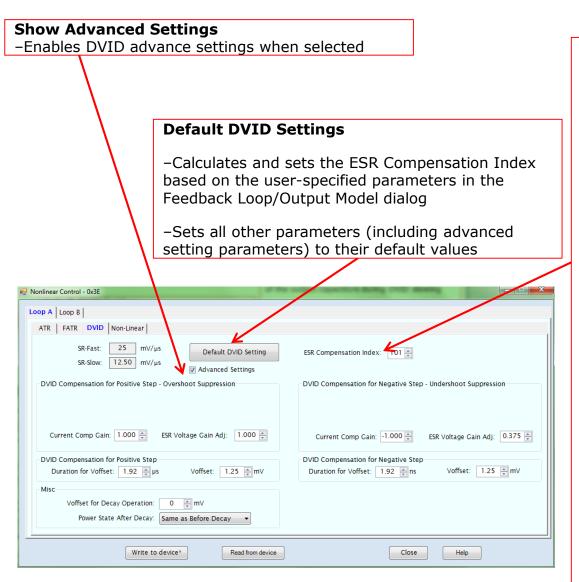

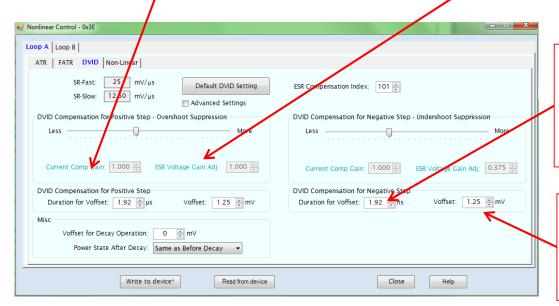

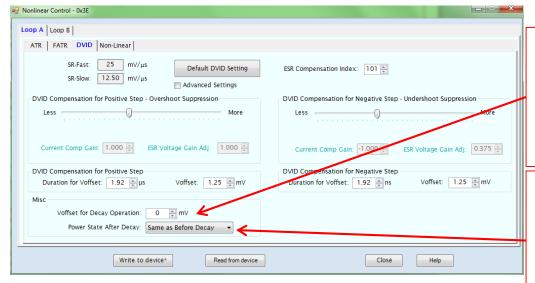

Dynamic VID (DVID) parameters to optimize the VR's response to the SetVID\_Fast/Slow/Decay commands

## **ESR Compensation Index**

- -Calculates the voltage offset caused by the ESR of the output capacitors during DVID slewing

- -Is inversely proportional to the Cout \*ESR time constant (*Cannot equal 0!*)

- -Decrease and re-adjust the DVID Compensation slider bars (when Advance setting box is not marked)

- •If fast response is needed or ring back follows the overshoot

- •Lowering this value forces the target voltage to ramp up/down faster that makes the response more aggressive and bigger overshoot if the sliders stay in the same position

- -Increase and re-adjust the DVID Compensation slider bars when Advance setting box is not marked

- •If there is a need to weaken the compensation

**Note**: The normal range for **ESR Compensation Index** is ~40 to ~130. Values below 40 often result in a very aggressive response and the ones bigger than 130 end up very small improvements.

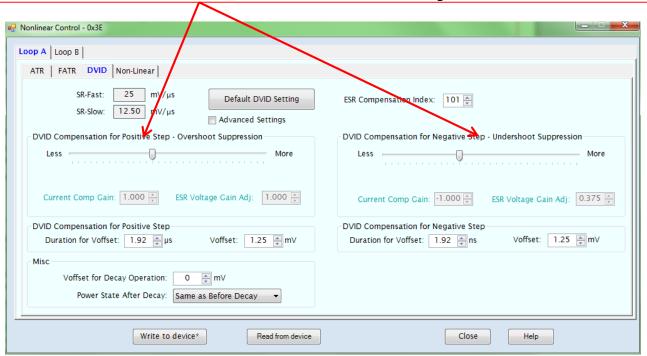

## **DVID Compensation slider bars**

- -Use to adjust Current Comp. Gain and ESR Voltage Gain Adjust in positive or negative step

- -Positive Step Overshoot Suppression

- •If the DVID response is slow, move the slider to the right to make it faster at the expense of a higher overshoot

- •If the DVID response is very aggressive, move the slider to the left to make it slower and have more overshoot suppression

- -Negative Step Undershoot Suppression

- •If a slower response and with less undershoot is desired, move the slider to the left (smaller index)

- •Move the slider to the right or left to obtain the desired response

-Slider bars are disabled and not visible when Advance Settings box is marked

### **Current Comp. Gain**

- -Use to compensate the voltage offset caused by the load-line effect on the output capacitor charging or discharging current during DVID slewing

- -Directly proportional to load-line and inversely proportional to ESR

- -Positive Step Overshoot Suppression

- •Usually ≥ 1 because faster response is desired

- Negative Step Overshoot Suppression

- •Usually ≤ 0 because response should be slowed down to prevent any undershoot, therefore it is suggested to be not fully compensated

## **ESR Voltage Gain Adj**

- -Used to compensate voltage offset caused by the output capacitors' ESR during DVID slewing

- -Positive Step Overshoot Suppression

- •Usually set to 1

- -Negative Step Undershoot Suppression

- •Usually set less than Positive Step Overshoot Suppression value

Copyrig CKAYAHO CWWWSWABAND - ATPHEOEDINHANCA!

#### **Duration for Voffset**

- -Time where the Voffset will be applied after the ramp completion

- -Independent settings for Positive and Negative Step

## Voffset

- -Offset amplitude added after the ramp completion

- -Independent settings for Positive and Negative Step

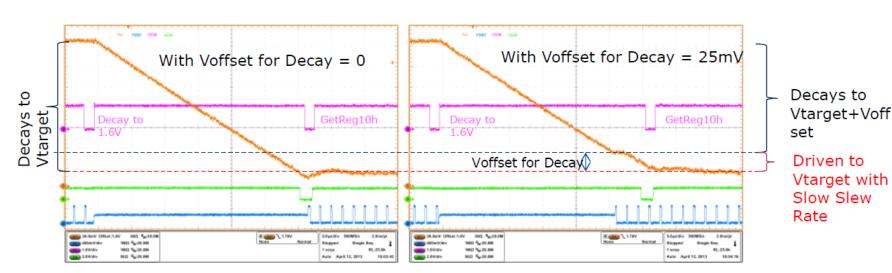

## **Voffset for Decay Operation**

-After the VR reaches the Vtarget + Voffset through decay, the VR will actively drive Vout and continue to ramp to the Vtarget with the specified number of phases for PS2, at slow slew rate

-Recommended value is 25mV

## **PowerState After Decay**

-Same as Before Decay - VR will keep the same PowerState after the decay as it had before decay. Normally for VR13 applications.

-PS2 - VR enters PS2 state after decay. Normally for IMVP8 applications.

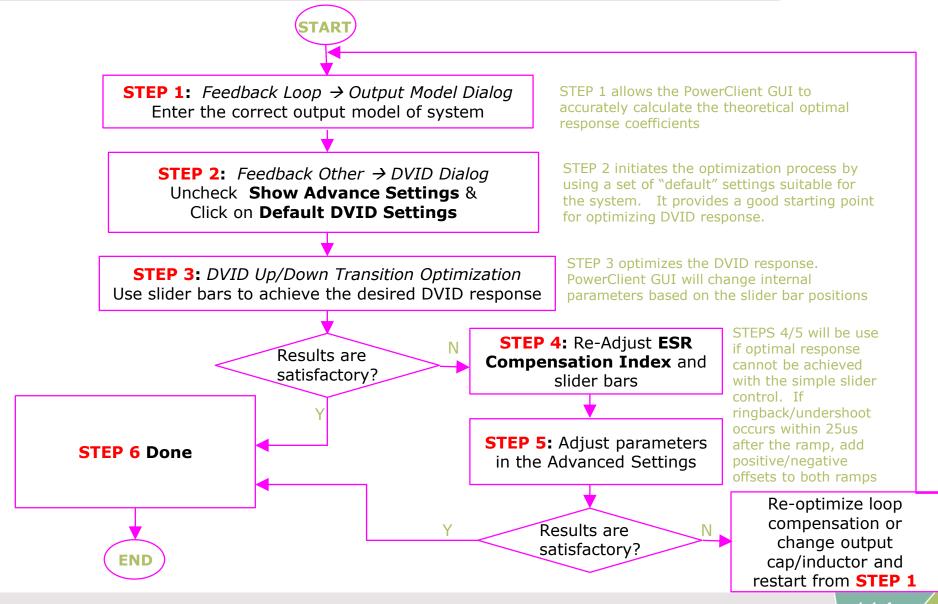

# Nonlinear Control... DVID Optimization Procedure

# Nonlinear Control... **DVID Optimization Procedure**

- If desired response cannot be achieved in **Step 5**

- -Re-adjust PID coefficients in the Feedback Loop/Compensation tab dialog. The current response is not well optimized.

- •An unstable system will cause undesired rings or oscillations

- •A very slow system cannot meet DVID timing requirements

- -Reduce output inductance or capacitance: Current introduced by very large output capacitance (C\*dv/dt) is very difficult to compensate for.

- •Extra current (energy stored in L) during a DVID up event will transfer to the output cap resulting in overshoot waveform

- •Large overshoot will accumulate more error in the PID which the loop has to remove, resulting in slight undershoot

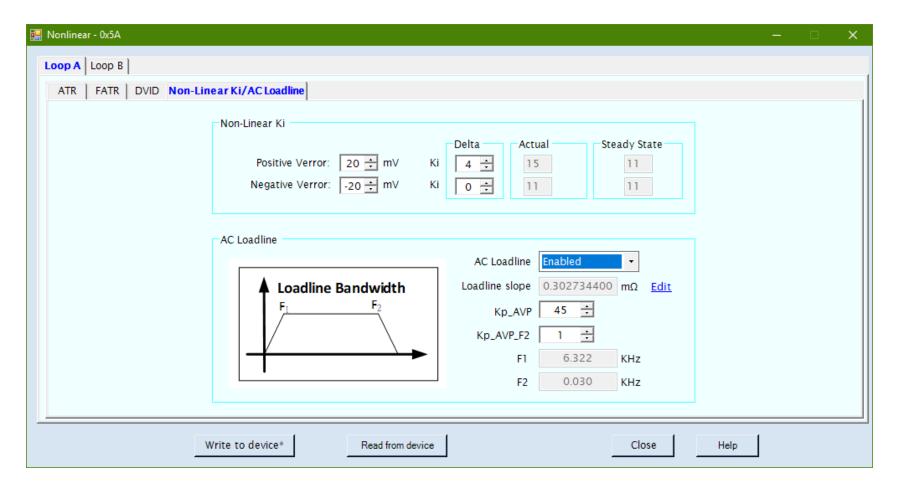

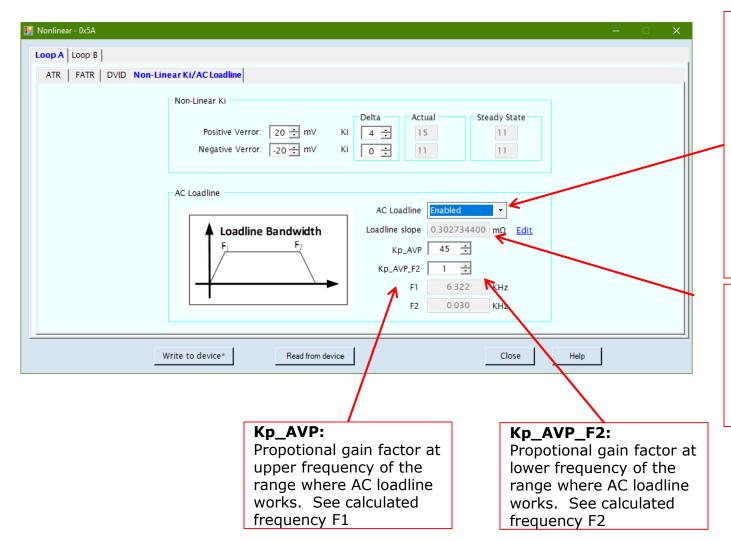

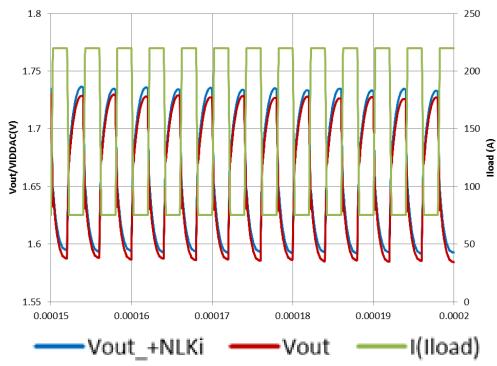

## Nonlinear Control... Non-linear

Non-Linear parameters to gain more undershoot or overshoot margin at high load repetition frequency. More explanation on next pages.

## Nonlinear Control... Non-linear

#### **Positive Verror:** Delta Ki: -Verror threshold to activate Ki change specified in -Ki change applied to the original Ki when Positive or Negative Verror is met Delta Ki **Actual:** 🖳 Nonlinear - 0x5A -Calculates and displays Loop A Loop B the actual Ki when the changes in **Delta** are ATR | FATR | DVID | Non-Linear Ki/AC Loadline applied Non-Linear Ki Steady State Actual Positive Verror: 20 🖶 mV 15 11 Negative Verror: -20 → mV 0 ÷ 11 11 AC Loadline Enabled AC Loadline Loadline slope 0.302734400 mΩ Edit Loadline Bandwidth 45 ÷ Kp\_AVP **Steady State:** Kp\_AVP\_F2 -Displays the original 6.322 KHz steady state Ki 0.030 KHz Write to device Read from device Close Help

## **Negative Verror:**

-Verror threshold to activate Ki change specified in Delta Ki

Note: Verror threshold should be larger than output ripple amplitude to avoid false trigger

## Nonlinear Control... AC loadline

#### AC loadline:

Enable or Disable the AC loadline function.

AC loadline add a slope to a loadline between 2 frequencies. While still having the regular performance at steady load for applications that normally do not use loadline.

AC loadline <u>may</u> improve higher frequency load transients to have less over/undershoot.

## Loadline slope:

Slope of the AC loadline between selected frequencies. Notice that when AC loadline is enabled there is no loadline at lower frequencies.

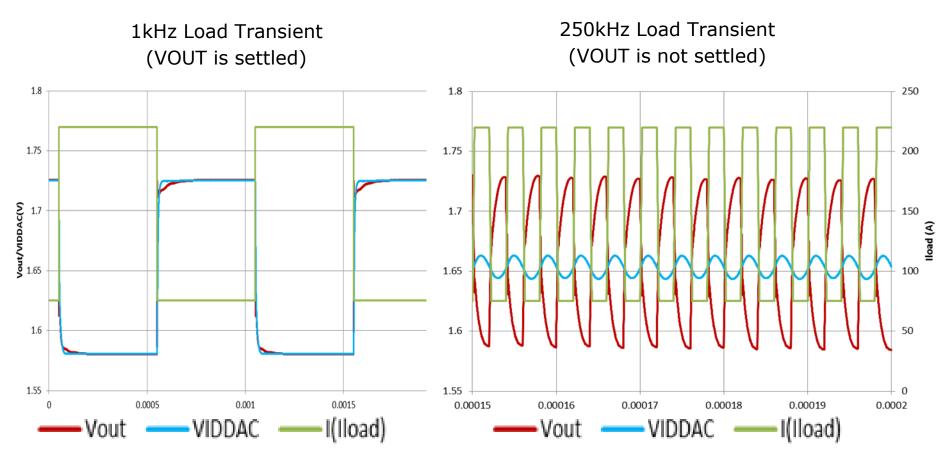

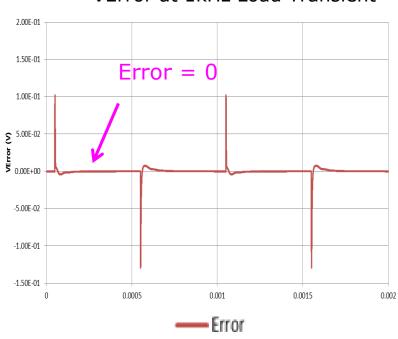

# Nonlinear Control: Non-Linear Background

> At high load repetition frequency, VOUT cannot settle within one load cycle

# Nonlinear Control: Non-Linear Background

For high frequency transient response the error can not be reduced to 0 before next cycle of transient load occurs

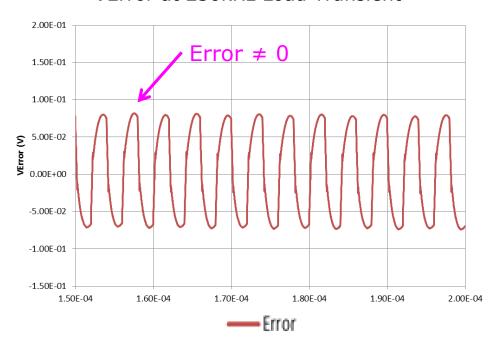

## VError at 1kHz Load Transient

## VError at 250kHz Load Transient

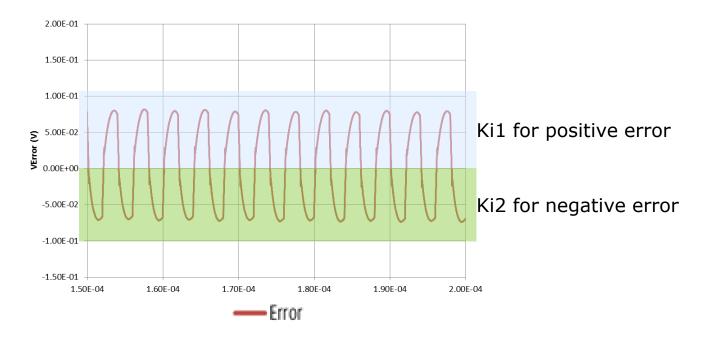

# Nonlinear Control: Non-Linear Background

2020-04-30

Compensator I term is proportional to the integrated error

$$I term = Ki * \int Error dt$$

- Xi for positive and negative Verror can be specified separately to influence the I term:

- If Ki1 > Ki(original) AND Ki2 ≤ Ki(original), VOUT will be shifted up

- If Ki1 ≤ Ki(original) AND Ki2 > Ki(original), VOUT will be shifted down

# Nonlinear Control: Non-Linear example

If more undershoot margin is needed, we can specify a positive Ki to shift VOUT up

**Infineon Proprietary**

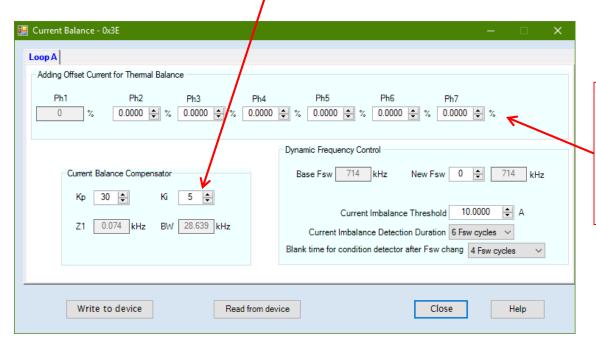

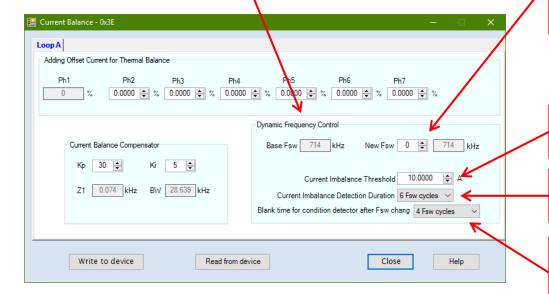

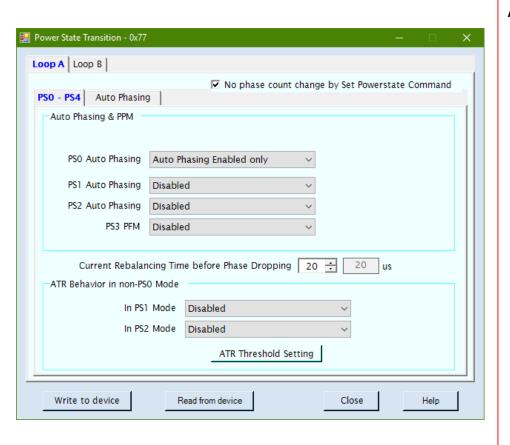

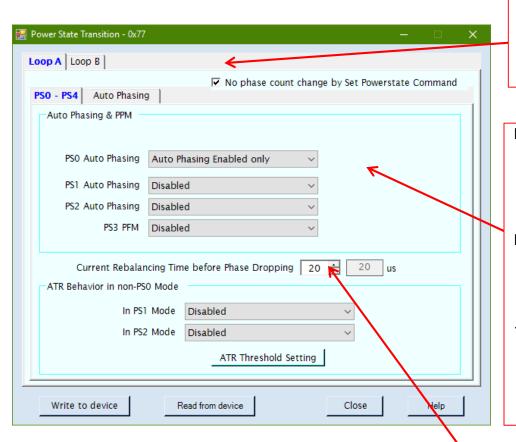

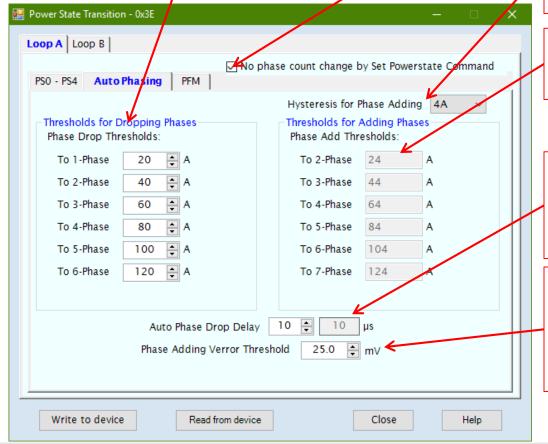

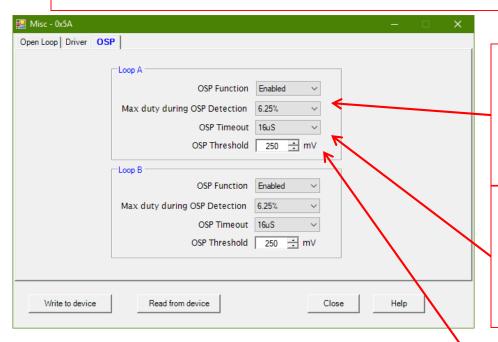

# Agenda