#### **Features**

- Wide Output Current Range: 8A

- Wide Input Voltage Range: 3V~28V

- Adjustable 0.8V~20V Output Range

- ±1% Output Voltage Accuracy over Line and Load

- Constant-on-time control scheme for fast transient and high Efficiency

- Programmable Operation Frequency from 100kHz to 600kHz

- Integrated 20 mΩ at LDO=5V N-Channel

MOSFET For High Side

- Integrated 9.5 mΩ at LDO=5V N-Channel MOSFET For Low Side

- Selectable Forced PWM or automatic PFM/PWM mode

- Power Good Indicator

- Under-Voltage Protection

- Over-Voltage Protection

- FB Short Protection

- Internal 5V Pre-regulator

- External Adjustable Soft-Start and Soft-Stop

- Over Temperature Protection

- Over Current Protection

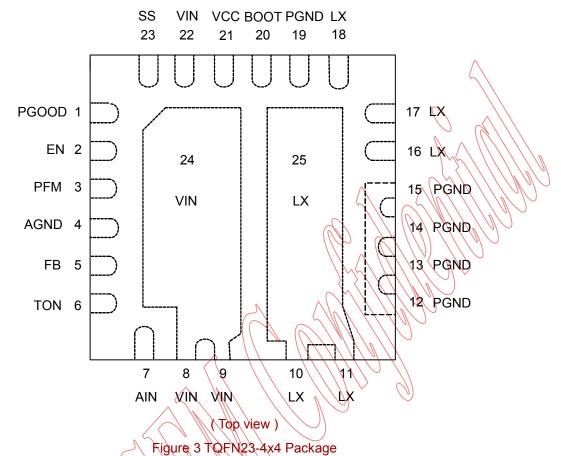

- TQFN23-4x4 package

- Green Product (RoHS, Lead-Free)

Halogen-Free Compliant)

## **Applications**

- Notebook computers

- CPU core/IO Supplies

- Chip/RAM Supplies $^{\downarrow}$

#### **General Description**

The GS9238 is small size chip with a relative constant on-time synchronous buck switching converter suitable for applications in notebook computers and other battery operated portable devices. Features include wide input voltage range, high efficiency and fast dynamic response The GS9238 has a unique power save mode, which can save battery power supply by decreasing frequency when load current falls down below preset critical current point.

The fast dynamic transient response means that buck converter applications based on GS9238 will provide about 100ns-order response to load when output voltage falls down or rises up. The frequency will increase or decrease to meet the change in output load. Moreover, the GS9238 will take the same method to regulate the output voltage when input voltage changes. When transient response regulated, the converter will maintain a new steady-state operation. Both the transient response state and the new state, the GS9238 always has the same on-time width.

The GS9238 is suitable for the solutions which the output voltage is between 0.8V and 20V. An external setting resistor and output voltage can set the on-time width and frequency for the converter. Additional features include current limit, soft-start, over-voltage and under-voltage protection, a Power Good flag and soft discharge upon shutdown. The GS9238 is available in package TQFN23-4x4.

This document is NIKO-SEM's confidential information. Anyone having confidential obligation to NIKO-SEM shall keep this document confidential. Any unauthorized disclosure or use beyond authorized purpose will be considered as violation of confidentiality and criminal and civil liability will be asserted.

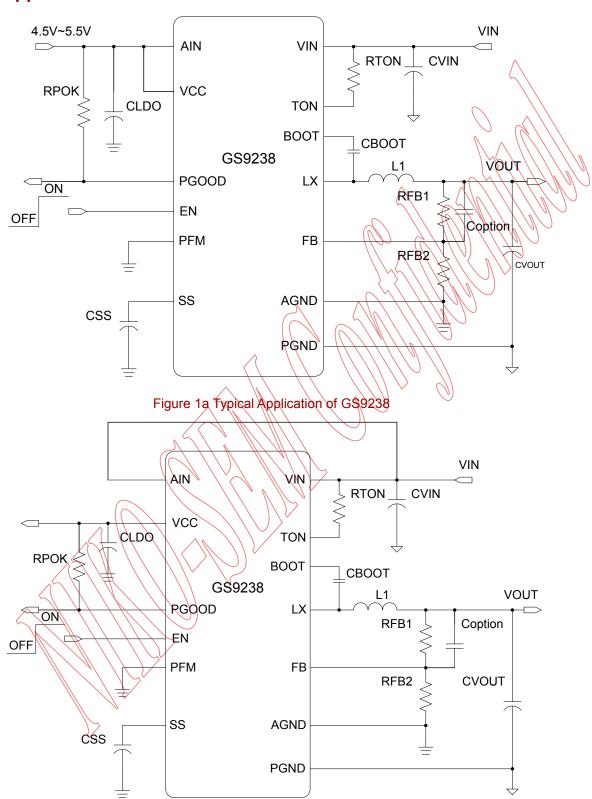

## **Typical Application**

Figure 1b Typical Application of GS9238

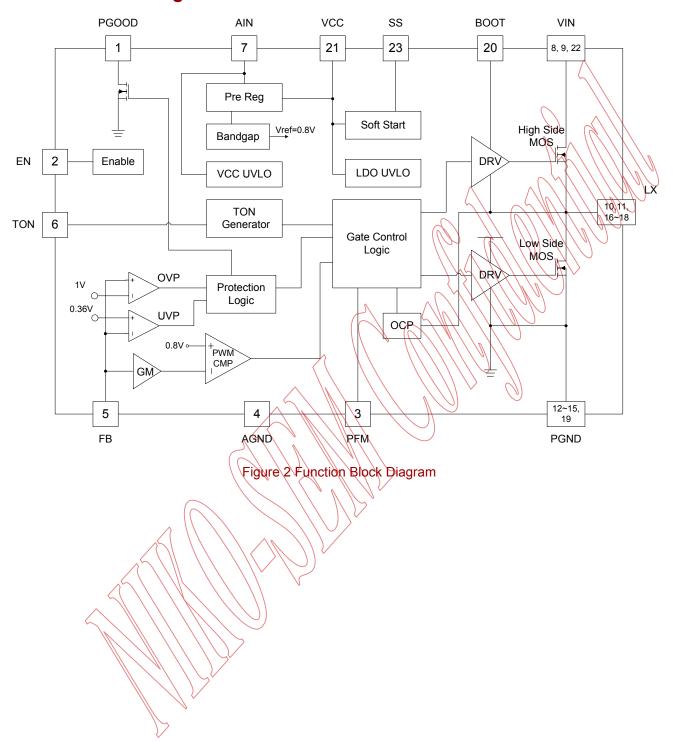

## **Function Block Diagram**

# **Pin Configuration**

**Pin Descriptions**

| Pin Descriptions |         |        |                                                            |

|------------------|---------|--------|------------------------------------------------------------|

| No.              | Name    | 1/0    | Description                                                |

| 1 4              | PGOOD   |        | Power Good Signal Output. PGOOD is an open-drain           |

|                  |         |        | output used to indicate the status of the output voltage.  |

| 2 ^              | EN      |        | Buck Enable Control Pin. EN=Low, Shutdown; EN=High,        |

|                  |         |        | Power On.                                                  |

|                  |         | $\geq$ | PFM Selection Input. Connect PFM pin to VCC/VIN for        |

| 3                | REM!    | I      | forced PWM operation. Connect PFM to ground for PFM        |

|                  |         |        | operation.                                                 |

| 4                | AĞND    | 0      | Analog Ground                                              |

| 5                | √<br>FB |        | Feedback Input. Adjust the output voltage with a resistive |

| 5                | ГБ      | ı      | voltage-divider between the regulator's output and AGND.   |

| 6                | TON     |        | On-Time Setting Input. Connect a resistor between VIN      |

| 0                | TON     |        | and TON to set the on time width.                          |

| 7                | AIN     |        | Supply Input for internal analog circuitry.                |

# High Performance Single Synchronous Buck Converter

| 8, 9, 22, 24          | VIN  | 1   | Supply Input. VIN is the regulator input. All VIN pins must be connected together.               |

|-----------------------|------|-----|--------------------------------------------------------------------------------------------------|

| 10, 11, 16, 17,18, 25 | LX   | I/O | Upper Driver Floating Ground for Buck Controller. Connect to an external inductor.               |

| 12,13, 14, 15, 19     | PGND | 0   | Power Ground.                                                                                    |

| 20                    | воот | I   | Bootstrap Capacitor Connection. Connect a capacitor between BOOT and LX Pin.                     |

| 21                    | VCC  | 0   | Internal Linear Regulator Output.                                                                |

| 23                    | SS   | I/O | Soft-Start Time Setting Pin. Connect a capacitor between SS and AGND to set the soft-start time. |

# Ordering Information GS9238TQ-R

1. Package 2. Shipping

| No | Item     | Contents       |

|----|----------|----------------|

| 1  | Package  | TQ: TQFN23-4x4 |

| 2  | Shipping | R: Tape & Reel |

Example: GS9238 TQFN23-4x4 Tape & Reel ordering information is "GS9238TQ-R"

# **Absolute Maximum Rating (Note 1)**

| Parameter                                         | Symbol                | Limits                                  | Units       |

|---------------------------------------------------|-----------------------|-----------------------------------------|-------------|

| VIN, AIN to GND                                   | $V_{IN}, V_{AIN}$     | -0.3 ~ 30                               | V           |

| TON to GND                                        | $V_{TON}$             | -0.3 ~ 30                               | V           |

| VCC, VPG to GND                                   | $V_{CC}, V_{PG}$      | -0.3 ~ 6                                | V           |

| EN/PFM to GND                                     | $V_{EN}, V_{PFM}$     | -0.3 ~ 30                               | \           |

| FB to GND                                         | $V_{FB}$              | -0.3 ~ 6                                | // <b>K</b> |

| BOOT Voltage                                      | $V_{BOOT\text{-}GND}$ | -0.3 ~ 40                               |             |

| BOOT to LX Voltage                                | $V_{BOOT	ext{-}LX}$   | -0.3 ~ 6                                | JV          |

| LX to GND DC                                      | V                     | \(\)\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\  | )<br>V      |

| <200ns                                            | $V_{LX}$              | \\ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | V           |

| Package Power Dissipation at T <sub>A</sub> ≤25°C | $P_{D\_TQFN23-4x4}$   | 3546                                    | mW          |

| Junction Temperature                              | L.                    | 150                                     | $^{\circ}$  |

| Storage Temperature                               | Tsto                  | 150                                     | $^{\circ}$  |

| Lead Temperature (Soldering) 10S                  | TLEAD \               | 260                                     | °C          |

| ESD (Human Body Mode) (Note 2)                    | V <sub>ESD_HBM</sub>  | 2K                                      | V           |

| ESD (Machine Mode) (Note 2)                       | V <sub>ESD_MM</sub>   | 200                                     | V           |

Thermal Information (Note 3)

| Parameter                   |            |  | Symbol                     | Limits | Units |

|-----------------------------|------------|--|----------------------------|--------|-------|

| Thermal Resistance Junction | to Ambient |  | θ) <sub>A_TQFN23-4x4</sub> | 28.2   | °C/W  |

**Recommend Operating Condition (Note 4)**

| Parameter            | Symbol            | Limits                       | Units      |

|----------------------|-------------------|------------------------------|------------|

| VIN to GND (Note 5)  | V <sub>IN</sub>   | 3~28                         | V          |

| AIN to GND (Note 5)  | $V_{AIN}$         | 6~28                         | V          |

| VCC to GND           | $V_{VCC}$         | 4.5~5.5                      | V          |

| EN, PFM to GND       | $V_{EN}, V_{PFM}$ | $V_{EN} = V_{PFM} = V_{AIN}$ | V          |

| Junction Temperature | $T_J$             | -40 ~125                     | $^{\circ}$ |

| Ambient Temperature  | T <sub>A</sub>    | -40 ~ 85                     | °C         |

Feb-17

# **Electrical Characteristics**

(RTON=100KOhm,  $V_{IN}=V_{AIN}=V_{EN}=12V$ ,  $T_A$  =25°C, unless otherwise specified)

| Parameter                   | Symbol                   | Conditions                                  | Min         | Тур                                    | Max | Units         |

|-----------------------------|--------------------------|---------------------------------------------|-------------|----------------------------------------|-----|---------------|

| Supply Voltage (VAIN        |                          |                                             | $\triangle$ |                                        |     |               |

| Under voltage lock          | V <sub>AIN_UVLO</sub>    |                                             |             | 5.5                                    |     | V             |

| out (Rising)                | V AIN_UVLO               |                                             |             | 5.5                                    |     |               |

| UVLO Hysteresis             | V <sub>AIN_UVLOHYS</sub> |                                             |             | 0.2                                    |     | V             |

| <b>5V Pre-regulator</b> (VV | cc)                      |                                             |             | $\sim$                                 | 1   | 1/1/2         |

| Output Voltage              | $V_{VCC}$                |                                             |             | 5.15                                   |     | V             |

| Under voltage lock          | Vyodania                 |                                             | D           | 4.15                                   |     | )<br><b>V</b> |

| out (Rising)                | V <sub>VCC_UVLO</sub>    |                                             |             | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |     | V             |

| UVLO Hysteresis             | V <sub>VCC_UVLOHY</sub>  |                                             |             | 0.3                                    |     | V             |

| Reference Voltage           |                          |                                             |             | 11/1                                   |     |               |

| FB Reference                |                          |                                             |             |                                        |     |               |

| Voltage                     | $V_{FB}$                 | V <sub>VCC</sub> =5V                        |             | 0.8                                    |     | V             |

| Control Input               |                          |                                             |             | A (1)                                  |     |               |

| EN Logic Low                | M                        | EN Falling                                  |             |                                        | 0.0 | V             |

| Voltage                     | V <sub>EN_L</sub>        | ENFAIIII                                    |             |                                        | 0.6 | V             |

| EN Logic High               | \(                       | EN Rising                                   | 1.6         |                                        |     | <b>\</b>      |

| Voltage                     | V <sub>EN_H</sub>        | EN RISHING                                  | 1.0         |                                        |     | V             |

| PFM Logic Low               |                          | PFM Falling                                 |             |                                        | 0.6 | V             |

| Voltage                     | VPEM_L                   | Friviraling                                 |             |                                        | 0.0 | V             |

| PFM Logic High              |                          | DEM Dising                                  | 2.5         |                                        |     | V             |

| Voltage \(\)                | KPWW7H                   | PFM Rising                                  | 2.5         |                                        |     | V             |

| PGOOD Signal                |                          |                                             |             |                                        |     |               |

| PGOOD Low                   | VPG                      | I <sub>PG</sub> =1mA                        |             |                                        | 0.5 | V             |

| Voltage                     | VPG                      | IPG-IIIIA                                   |             |                                        | 0.5 | V             |

| PGOOD Leakage               | lrg_leak                 | V <sub>PG</sub> =5V                         |             | 1                                      |     | uA            |

| Current                     | IKO_LEAN                 | v PG-O v                                    |             | l<br>                                  |     | uД            |

|                             | VPG_H                    | $V_{FB}$ >125%, $V_{PG}$ go to              |             | 125                                    |     | %             |

| PGOOD Threshold             | VPG_H                    | Low                                         |             | 120                                    |     | 70            |

| 1 GOOD HIRSHOID             | \/pa :                   | V <sub>FB</sub> >90%, V <sub>PG</sub> go to |             | 90                                     |     | %             |

|                             | VPG_L                    | High                                        |             | 90                                     |     | /0            |

| PGOOD Fault Delay           | Tpg                      | PG debounce time                            |             | 20                                     |     | us            |

| <b>Current Parameters</b> |                                        |                                                                                                                                    |            |                                     |                                       |          |

|---------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------|---------------------------------------|----------|

| Quiescent Current         | $I_{Q}$                                | $V_{FB} = 0.85V, V_{IN} = 12V$                                                                                                     |            | 870                                 |                                       | uA       |

| Soft start current        | Iss                                    | V <sub>SS</sub> =0                                                                                                                 |            | 10                                  |                                       | uA       |

|                           |                                        | $V_{EN}$ =0, $I(AIN)$                                                                                                              |            | 4                                   | $\wedge$                              | uA       |

| Shutdown Current          | I <sub>SHTDN</sub>                     | $V_{EN}$ =0, $I(TON)$                                                                                                              |            |                                     | 0.01                                  | uA       |

|                           |                                        | V <sub>EN</sub> =0, I(EN)                                                                                                          | -2         | -1                                  |                                       | uA       |

| Logic Input Current       | len                                    | VAIN= VEN=12V                                                                                                                      |            | 13                                  | $\langle \langle     \rangle \rangle$ | \\uA     |

| FB Input Bias<br>Current  | I <sub>FB</sub>                        | FB=0.8V                                                                                                                            | -0.1       | 0.001                               | 0.1                                   | UA       |

| System Time & Driv        | er On-Resist                           | tance                                                                                                                              |            |                                     |                                       | <u> </u> |

| On-Time                   | $T_{ON}$                               | $V_{IN}$ =12V, $V_{FB}$ =0.79V,                                                                                                    |            | (300                                |                                       | ns       |

| On Time                   | I ON                                   | R <sub>TON</sub> =100K,V <sub>OUT</sub> =1.2V                                                                                      | \_         |                                     |                                       | 110      |

| Minimum Off-Time          | $T_{OFFMIN}$                           | $V_{IN}$ =12V, $V_{FB}$ =0.79V,                                                                                                    |            | 440                                 |                                       | ns       |

| William Cit Time          | OFFININ                                | R <sub>TON</sub> =100K                                                                                                             |            | 1///                                |                                       | 110      |

| High Side MOS             | $R_{	extsf{DSH}}$                      | BOOT-LX=5V                                                                                                                         |            | 20                                  |                                       | mohms    |

| RDSON                     | 1 10011                                |                                                                                                                                    |            |                                     |                                       |          |

| High Side Leakage         | I <sub>LEAKH</sub>                     |                                                                                                                                    |            | 10                                  |                                       | uA       |

| Low Side MOS              | $R_{DSL}$                              | VCC-GND=5V                                                                                                                         | $\bigcirc$ | 9.5                                 |                                       | mohms    |

| RDSON                     | (                                      |                                                                                                                                    |            |                                     |                                       |          |

| Low Side Leakage          | I <sub>LEAKL</sub>                     |                                                                                                                                    |            | 10                                  |                                       | uA       |

| Current Sensing           |                                        |                                                                                                                                    |            |                                     |                                       |          |

| Current                   | I LIM                                  | GND-LX                                                                                                                             | 8          |                                     |                                       | Α        |

| Limit(Rising)             |                                        |                                                                                                                                    |            |                                     |                                       |          |

| Zero Crossing             | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | GND-LX                                                                                                                             | -10        |                                     | 10                                    | mV       |

| Threshold Control Parks   |                                        |                                                                                                                                    |            |                                     |                                       |          |

| Voltage Fault Prote       | ction                                  | Manager at V weith                                                                                                                 |            |                                     |                                       |          |

| LIVO Throughold           |                                        | Measure at V <sub>FB</sub> , with                                                                                                  |            | 45                                  |                                       | 0/       |

| UVP Threshold             | V <sub>UV</sub> TH)                    | respect to reference                                                                                                               |            | 45                                  |                                       | %        |

|                           |                                        | voltage                                                                                                                            |            |                                     |                                       |          |

| UVP Blank Time            | $\searrow_{T}$                         | From Enable to UVP 80mV <v<sub>FB<uvp< td=""><td></td><td>1.6x10<sup>8</sup>xC<sub>S</sub></td><td></td><td>me</td></uvp<></v<sub> |            | 1.6x10 <sup>8</sup> xC <sub>S</sub> |                                       | me       |

| OVE DIATIK TITIE          | V T <sub>UV_B</sub>                    | Threshold                                                                                                                          |            | S                                   |                                       | ms       |

|                           |                                        | Force V <sub>FB</sub> below UVP                                                                                                    |            |                                     |                                       |          |

| UVP Fault Delay           | $T_{UV_{D}}$                           | threshold                                                                                                                          |            | 20                                  |                                       | us       |

|                           |                                        | u ii estiloid                                                                                                                      |            |                                     |                                       |          |

# High Performance Single Synchronous Buck Converter

|                        |                       | Measure at V <sub>FB</sub> , with |  |                                                                                                     |                                          |       |

|------------------------|-----------------------|-----------------------------------|--|-----------------------------------------------------------------------------------------------------|------------------------------------------|-------|

| OVP Threshold          | $V_{OV\_TH}$          | respect to reference              |  | 125                                                                                                 |                                          | %     |

| - Thi concid           | VOV_IH                | voltage                           |  | 120                                                                                                 |                                          | ,0    |

|                        |                       |                                   |  |                                                                                                     |                                          |       |

| OVP Delay              | Т                     | Force V <sub>FB</sub> above OVP   |  | 20                                                                                                  |                                          | us    |

| OVI Delay              | $T_{OV_D}$            | Threshold                         |  | 20                                                                                                  |                                          | us    |

| Over Temperature S     |                       |                                   |  |                                                                                                     | \                                        |       |

| Thermal Shutdown       | <b>-</b>              |                                   |  | 450                                                                                                 | , 4/                                     |       |

| Threshold              | $T_{TSDN}$            |                                   |  | 150                                                                                                 | <u> ۱۲/ ///</u>                          | \\\°C |

| Thermal Shutdown       | +                     |                                   |  | A 00 A                                                                                              |                                          |       |

| Hysteresis             | T <sub>HYS_TSDN</sub> |                                   |  | 20                                                                                                  |                                          | ///c  |

| <b>Bootstrap Diode</b> | Bootstrap Diode       |                                   |  | 7//////                                                                                             | 1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/ | )     |

| Internal Boost         |                       |                                   |  | $\setminus \langle \langle \langle \langle \langle \langle \rangle \rangle \rangle \rangle \rangle$ |                                          |       |

| Charging Switch        | $R_{BT\_D}$           | VCC to BOOT, 10mA                 |  |                                                                                                     | 120                                      | ohms  |

| On-Resistance          |                       |                                   |  |                                                                                                     |                                          |       |

Note 1. Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied.

Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3.θ<sub>JA</sub> is measured in the natural convection at T<sub>A</sub>=25°C on a high effective thermal conductivity test board (4 Layers, 2S2P) of JEDEC 51-7 thermal measurement standard.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5 Recommend the Pulse time < 100ns when VIN over than 30V.

Note 6 If V(BOOT)-V(LX)<4V, a boot diode is recommended.

#### **Typical Characteristics**

# On-time vs. Input Voltage VIN=12V, RTON=100K, Vout=1.2V

# On-time vs. Input Voltage 1400 1200 1000 800 400 200 0 3 8 13 18 23 28 Input Voltage (V)

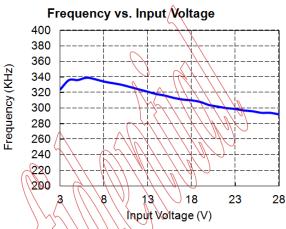

# Frequency vs. Input Voltage VIN=12V, RTON=100K, Vout=1.2V

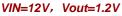

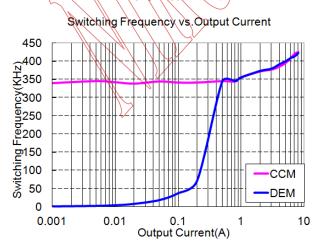

#### Frequency vs. Load Current

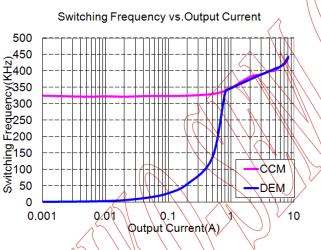

#### **VOUT Efficiency vs. Load Current**

VIN=12V, Vout=1.2V

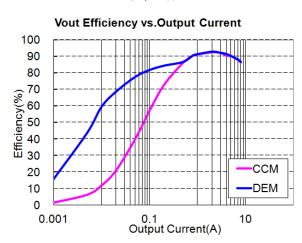

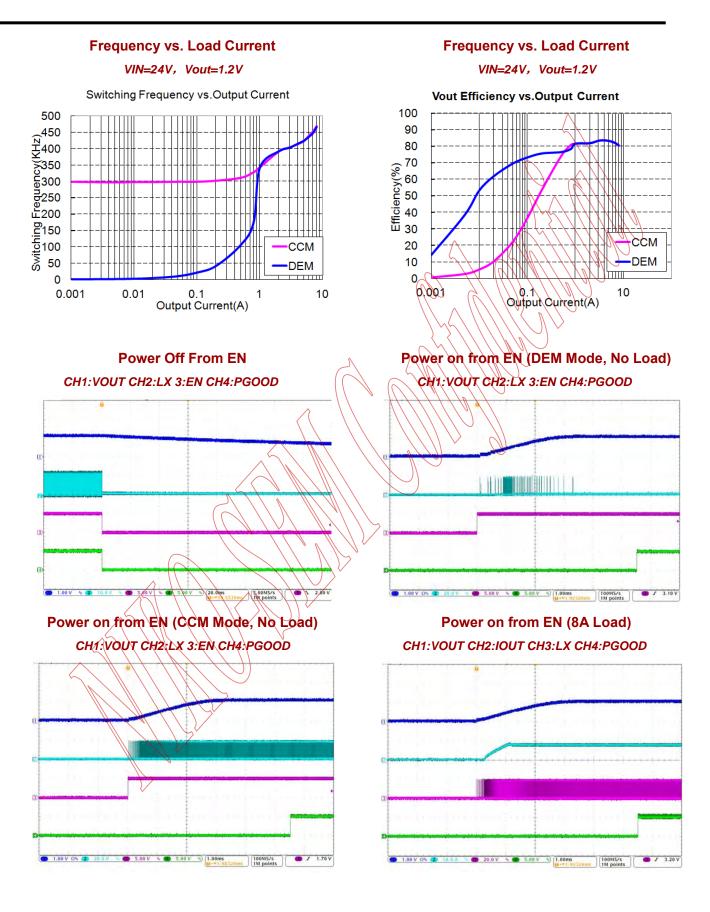

# Frequency vs. Load Current

#### VIN=5V, Vout=1.2V

#### **OUT Efficiency vs. Load Current**

#### VIN=5V, Vout=1.2V

Feb-17

Feb-17

### **Application Information**

The GS9238 is small size chip with a relative constant on-time synchronous buck switching converter suitable for applications in notebook computers and other battery operated portable devices. Features include wide input voltage range, high efficiency and fast dynamic response.

#### **System Clock Generator and PWM Control**

The on-time of GS9238 can be set by an external setting resistor from input voltage to TON Pin. The converter maintains the on-time width as loop feedback path exists between the GS9238 converter, low pass filter and voltage divider. For a given input voltage buck application, the feedback maintains the constant on-time width. Due to the constant resistor and input voltage, the GS9238 based buck converter has the relative constant frequency. Moreover, the GS9238 can increase the duty-cycle automatically as input voltage falls down. Because of the constant on-time in each switching period, the converter maintains the relative frequency when the input voltage changes

At the beginning of each switching cycle, upper power MOSFET is turned on, after typical fixed on-time, the upper MOSPET is turned off, and then lower power MQ\$FET is turned on after internal dead time. The upper MOSPET will not be turned on at the beginning of next cycle until output voltage falls down below the preset voltage and the dead time passes. The same events repeat the following switching cycles. To avoid the surge inductor current during large load transient, a minimum Off-time is added. Typical minimum off-time is around 440ns. The too small on-time can affect soft-start and anti-noise ability, so in order to avoid the on-time too small to be eliminated; a minimum on-time is set to around 110ns. This should to be noted in the small duty applications.

#### **High Side Switch On-Time Count**

The on-time is decided by the external setting resistor, and the input voltage. Looking at the TON pin, the input voltage is converted to current which is inversely proportional to itself by dividing the external setting resistor. The input voltage-proportional current is used to charge an internal capacitor from zero volts. When the voltage between two terminals of the capacitor reaches to the internal setting voltage, on-time one-shot pulse is generated, and then upper power MOSFET is turned on.

We can count the on-time and switching frequency according to the equations below:

Ton=(14.4p×R+on+1.44u) / (VIN-0.8)

Then, the switching frequency is:

$F_{sw} = V_{OUT} / (V_{IN} \times T_{ON})$

$R_{TON}$  is a resistor connected from the input supply (VIN) to the TON pin.

For heavy load (more than 8A) application, due to ground bounced and the high impedance of  $R_{TON}$ , the TON pin should always be bypassed to GND using a several nF-order ceramic capacitor for reliable system operation.

#### **EN, PFM/PWM Mode and Shutdown Soft-Discharge**

The EN pin enables the power supply. When EN is tied to VIN and the PFM Pin is pulled low, the GS9238 converter is enabled and diode-emulated mode (DEM, which is power save mode) will be also enabled. When the PFM pin is pulled high, it will force the converter into PWM mode.

In PFM(DEM) mode, when the loads goes low, GS9238 starts power save mode in order to maintain the on-time and decrease the system clock frequency to skip PWM pulses for better efficiency. If DEM Mode is enabled, the GS9238 zero crossing comparator will sense the inductor current and judge its value by comparing the LX node (LX) to PGND. Once the LX node voltage is

Rev.:1P8 GStek series equal to the PGND node voltage, the converter will enter the DEM Mode and turn off the low side power MOSFET. The boundary of PWM to PFM mode can be calculated by the output current.

$$I_{OUT(Boundary)} = \frac{V_{IN} - V_{OUT}}{2L} \times \frac{1}{F_{SW}} \times \frac{V_{OUT}}{V_{IN}}$$

As the load current is further decreased, it takes longer time to discharge the output capacitor to the level than required the next switching cycle. The on-time is kept the same as that in the heavy-load condition.

If the EN pin is pulled low, the GS9238 internal logic will shutdown the switching clock and stop the buck converter, and FB-Discharge Module works to discharge the related output voltage through the FB pin. This will ensure that the output is in a defined state next time when it is enabled. Since this is a soft discharge, that there are no dangerous negative voltage excursions to be concerned about. In order to maintain the correct function of the soft-discharge module, the chip power supply must be online.

#### **VOUT Drop Function**

The GS9238 builds in a Vout voltage drop function for CCM mode operation. The drop function will make the Vout voltage deviate the voltage set by FB resistor calculated from 0.8V reference. Different Vin and Vout voltage make different drop voltage. The drop voltage follows the equation below:

$$V_{Drop} = -30m V \times \left(1 - \frac{8}{9} \times \frac{V_{IN}}{V_{IN}} + \frac{V_{OUT}}{1.2} \times \frac{1.2}{V_{OUT}}\right) \times \frac{V_{IN} - 1.2}{10.8}$$

$$-5m V$$

#### **Output Voltage Selection**

The output voltage is set by the feedback resistors  $R_{FB1}$  and  $R_{FB2}$  of Figure1a and Figure1b. Because of the Vout Drop Function, the direct reference should plus the VDrop. So, the calculation of  $R_{FB1}$  should considerate the VDrop voltage. Therefore the  $R_{FB1}$

and R<sub>FB2</sub> can be set by the equation below:

Set R<sub>FB2</sub>, then

$$R_{FB1} = R_{FB2} \times \left( \frac{V_{OUT}}{0.8 + V_{DROP}} - 1 \right)$$

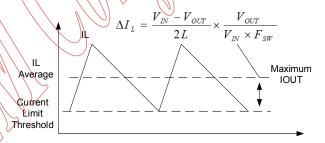

#### **Current Limit**

The GS9238 uses the on-state resistance of the low-side power MOSFET as a current limit threshold at least 8A. The current sensing circuit actually regulates the inductor valley current. This means that if the magnitude of the inductor valley current beyond the current limit, the PWM is not allowed to initiate a new switching cycle. The difference between the maximum output current and the valley current limit is depended on the ripple current of the inductor. It is diagramed by the graph below:

#### **Output Over-Voltage Protection**

When the output voltage rises up to 125% of the preset voltage, the internal fault-logic module delays about 20us and turns on the low side Power MOSFET. It stays latched on and the GS9238 is latched off until Power Reset or EN Reset.

#### **Output Under-Voltage Protection**

When the output voltage falls down to 45% of the preset voltage, the internal fault-logic module will delay about 20us and turns off both the high side and low side Power MOSFETs. Both switches stay latched off and the GS9238 is latched off until Power Reset or EN Reset. During soft-start, the UVP will be blanked, until soft-start procedure finished. The blank time depended on the value of the capacitor connected to SS Pin. But if

Rev.:1P8 GStek series Feb-17

# High Performance Single Synchronous Buck Converter

the output voltage rises up above the UVP threshold tolerance during the counter period, the UVP counter is released immediately.

#### **UVLO and Soft-Start**

An internal under voltage lockout (UVLO) module is used to sense the VCC power supply. The PWM converter is forbidden by the under voltage lockout module. When VCC rises about 4.15V, the GS9238 will initial the control logic circuitries and soft-start ramping generator, and then allows switching to occur. When VCC falls down to about 3.85V, the PWM converter is forbidden again.

When VAIN rises about 5.5V, the LDO output voltage (VCC) of GS9238 enables and regulates a 5.15V voltage. After VAIN falls down to 5.3V the LDO (VCC) will turn off.

After soft-start module starting, the GS9238 converter will release the current limit threshold followed the soft-start ramp. After UVP blanking time, the output under voltage protection and power good indicator is enabled.

#### **FB Short Protection**

Because the UVP protection is blanked during the soft-start period, if FB pin short to GND, the output voltage will increase continuously without OVP protection. It is a very dangerous condition. The GS9238 build in a safety protection scheme to avoid this situation. When soft-start procedure begins, the GS9238 monitors the SS Pin and FB Pin both, if the voltage of SS Pin is higher than 240mV and at the same time the voltage of FB Pin is lower than 80mV, after a few micro seconds delay, the fault logic will stop the switching cycle and latch on. Only Power on Reset and EN Reset can release this latch condition.

#### **Power Good Indicator**

PGOOD is actively held low in shut down and soft-start status. During the soft-start process, the PGOOD is an open-drain status. When the soft -start

is finished, the PGOOD is pulled high by external resistor. In normal operation, the PGOOD window is from 90% to 125% of the converter reference voltage. When the output voltage has to stay within this window, PGOOD signal will become high. When the output voltage outruns 90% or 125 % of the target voltage, PGOOD signal will be pulled low after about 20us delay. This delay prevent false PGOOD drop.

#### **External Devices Selection**

For loop stability, the 0 dB frequency (f0), defined in the follow equation:

$$f_0 = \frac{1}{2\pi \times RESR \times C_{OUT}} \times \frac{f_{SW}}{4}$$

The loop stability is determined by the output capacitor. Specialty polymer capacitors have  $C_{OUT}$  in the order of several 100uF and RESR in range of 10mohm is recommended. However, ceramic capacitors have f0 at more than 700 KHz, which is not recommended.

In order for the right regulate manner, the ripple voltage at the feedback pin (FB), should be approximately 15mV. This generates Vripple= (V<sub>OUT</sub>/0.8) ×15mV at the output node. The output capacitor RESR should meet this equation.

The external device selection is list below:

#### **Choose Feedback Voltage Divider Resistor**

Set R<sub>FB2</sub>=1K~20K ohm

$$R_{\text{FB1}} = R_{\text{FB2}} \times \left( \frac{V_{\text{OUT}}}{0.8 + V_{\text{DROP}}} - 1 \right)$$

#### **Choose RTON**

$$T_{ON(Max)} = \frac{1}{f_{SW}} \times \frac{V_{OUT}}{V_{IN(Min)}}$$

$$R_{TON(MAX)} = (V_{IN} - 0.8) \times 750K - 100K$$

#### **Choose Inductor**

Set the ripple current approximately 1/4 to 1/2 of the maximum output current. 1/3 is recommended. The recommended inductor can be calculated from the

Rev.:1P8 15 Feb-17 GStek series

output current, indicated by formula below

$$L_{IND} = \frac{3}{I_{IOUT(max)} \times f} \times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}}$$

For applications that require fast transient response with minimum VOUT overshoot, consider a smaller inductance than above. The cost of a small inductance value is higher steady state ripple, larger line regulation, and higher switching loss.

#### **Choose Output Capacitors**

$$RESR = \frac{1}{I_{ripple}} \times \frac{V_{OUT}}{0.8} \times 0.015$$

$$\approx \frac{3}{I_{OUT,(max)}} \times \frac{V_{OUT}}{0.8} \times 0.015$$

$$RESR \approx \frac{V_{OUT}}{I_{OUT(max)}} \times 75 (mohm)$$

Organic semiconductor capacitors or specialty polymer capacitors are recommended.

The GS9238 support pure MLCC because the benefit of the internal

#### **Choose Soft-Start Capacitor**

When SS ramp rise up to about 1.6V, the chip thinks the soft-start procedure is over, and then release the UVP protection function. At the same time, the VOUT voltage will reach the target set by the FB resistor divider. So, the total soft-start time is defined by the formula below:

$$T_{SS} = \frac{1.6 \times C_{SS}}{I_{SS}} = 1.6 \times 10^8 \times C_{SS} \text{(ms)}$$

Where, the unit of Tss is mS

For example, the typical Tss is equal to 1.6mS with 10nF  $C_{SS}$ .

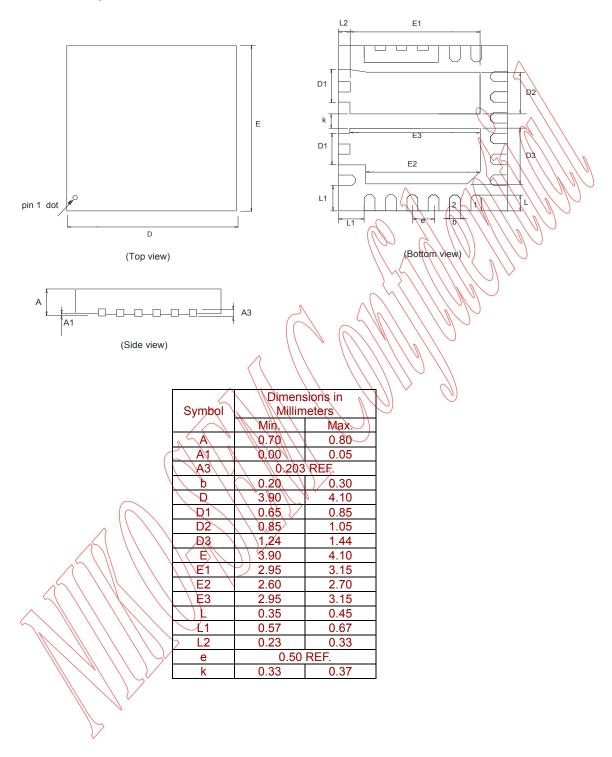

## Package Dimensions, TQFN23-4x4

#### <u>Note</u>

1. Min.: Minimum dimension specified.

2. Max.: Maximum dimension specified.

3. REF.: Reference. Normal/Regular dimension specified for reference.

Please read the notice stated in this preamble carefully before Admission e accessing any contents of the document attached. Admission of NIKO-SEM's statement therein is presumed once the document is released to the receiver.

Notice:

Firstly, NIKO SEMICONDUCTOR CO., LTD. (NIKO-SEM) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its information herein without notice.. And the aforesaid information does not form any part or parts of any quotation or contract between NIKO-SEM and the information receiver.

Further, no responsibility is assumed for the usage of the aforesaid information. NIKO-SEM makes no representation that the interconnect of its circuits as described herein will not infringe on exiting or future patent rights and other intellectual property rights, nor do the descriptions contained herein express or imply that any licenses under any NIKO-SEM patent right, copyright, mask work right, or other NIKO-SEM intellectual property right relating to any combination, machine, or process in which NIKO-SEM products or services are used.

Besides, the product in this document is not designed for use in life support appliances, devices, or systems where malfunction of this product can reasonably be expected to result in personal injury. NIKO-SEM customers' using or selling this product for use in such applications shall do so at their own risk and agree to fully indemnify NIKO-SEM for any damage resulting from such improper use or sale.

At last, the information furnished in this document is the property of NIKO-SEM and shall be treated as highly confidentiality; any kind of distribution, disclosure, copying, transformation or use of whole or parts of this document without duly authorization from NIKO-SEM by prior written consent is strictly prohibited. The receiver shall fully compensate NIKO-SEM without any reservation for any losses thereof due to its violation of NIKO-SEM's confidential request. The receiver is deemed to agree on NIKO-SEM's confidential request therein suppose that said receiver receives this document without making any expressly opposition. In the condition that aforesaid opposition is made, the receiver shall return this document to NIKO-SEM immediately without any delay.

Rev.:1P8 GStek series